# Integrated Shared-Memory and Message-Passing Communication in the Alewife Multiprocessor

by

### John David Kubiatowicz

S.B., Massachusetts Institute of Technology (1987) S.M., Massachusetts Institute of Technology (1993)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1998

© Massachusetts Institute of Technology, 1998. All rights reserved.

Signature of Author\_\_\_\_\_

Department of Electrical Engineering and Computer Science December 15, 1997

Certified by\_\_\_\_\_

Anant Agarwal Associate Professor of Computer Science and Electrical Engineering Thesis Supervisor

Accepted by\_\_\_\_\_

Arthur C. Smith Chairman, Departmental Committee on Graduate Students

#### Integrated Shared-Memory and Message-Passing Communication in the Alewife Multiprocessor

by

John David Kubiatowicz

Submitted to the Department of Electrical Engineering and Computer Science on December 15, 1997, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

To date, MIMD multiprocessors have been divided into two classes based on *hardware communication models*: those supporting *shared memory* and those supporting *message passing*. Breaking with tradition, this thesis argues that multiprocessors should integrate *both* communication mechanisms in a single hardware framework. Such integrated multiprocessors must address several architectural challenges that arise from integration. These challenges include the *User-Level Access problem*, the *Service-Interleaving problem*, and the *Protocol Deadlock problem*. The first involves *which* communication models are used for communication and *how* these models are accessed; the second involves avoiding *livelocks* and *deadlocks* introduced by multiple simultaneous streams of communication; and the third involves removing multi-node cycles in communication graphs. This thesis introduces these challenges and develops solutions in the context of Alewife, a large-scale multiprocessor. Solutions involve careful definition of communication semantics and interfaces to permit tradeoffs across the hardware/software boundary. Among other things, we will introduce the *User-Direct Messaging* model for message passing, the *transaction buffer* framework for preventing cache-line thrashing, and *two-case delivery* for avoiding protocol deadlock.

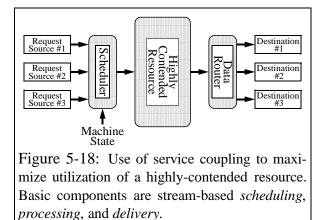

The Alewife prototype implements cache-coherent shared memory and user-level message passing in a single-chip *Communications and Memory Management Unit* (CMMU). The hardware mechanisms of the CMMU are coupled with a thin veneer of runtime software to support a uniform high-level communications interface. The CMMU employs a scalable cache-coherence scheme, functions with single-channel, bidirectional network, and directly supports up to 512 nodes. This thesis describes the design and implementation of the CMMU, associated processor-level interfaces, and runtime software. Included in our discussion is an implementation framework called *service coupling*, which permits efficient scheduling of highly contended resources (such as DRAM). This framework is well suited to integrated architectures.

To evaluate the efficacy of the Alewife design, this thesis presents results from an operating 32-node Alewife machine. These results include microbenchmarks, to focus on individual mechanisms, and macrobenchmarks, in the form of applications and kernels from SPLASH and NAS benchmark suits. The large suite of working programs and resulting performance numbers lead us to one of our primary conclusions, namely that *the integration of shared-memory and message-passing communication models is possible at a reasonable cost, and can be done with a level of efficiency that does not compromise either model.* We conclude by discussing the extent to which the lessons of Alewife can be applied to future multiprocessors.

Keywords: multiprocessor, shared memory, message passing, cache-coherence, Alewife machine

Thesis Supervisor: Anant Agarwal

Title: Associate Professor of Computer Science and Electrical Engineering

# Acknowledgments

As I sit here in Harvard Square at my favorite cafe (Au Bon Pain), I think back to the long and arduous path that I have taken. Today is unseasonably warm, even as trees are caught between the riotous colors of autumn and the stark lines of winter. The last 10 years have seen tremendous growth in my understanding as a general "systems" person, and I can only attribute this to the number of people who have given me "enough rope", as it were, to jump forward. A few stand out in my mind, however ...

First and foremost, my advisor, Anant Agarwal has given me more space and opportunity than any student could ever hope to acquire during the course of many graduate degrees. Over the years, we have clashed over philosophy, agreed vehemently over architecture, and enjoyed a healthy mutual respect that began from the day I accidentally wandered into his office. I have yet to encounter someone with a stronger mystical connection with the universe, *i.e.* the ability to make a counterintuitive conclusion based on no data which, upon further investigation, proved to be true beyond a measure of doubt. I can only hope to develop some small fraction of his intuition in the years to come. To a mentor, friend, colleague, and (oh yeah) advisor, I offer my heartfelt thanks.

In the late eighties, Dan Geer offered me a position at Project Athena, based only on an interview. At the time, I was a brash new graduate of MIT with absolutely no experience writing applications under UNIX, much less delving into its depths. The resulting two years there gave me a strong understanding of operating systems that I would never have gained otherwise.

To my colleagues in the Alewife group, I offer my heartfelt thanks. Without qualification, I can say that I was honored to work with each and every member of the Alewife group. The original core group, consisting of David Chaiken, Kirk Johnson, David Kranz, Beng-Hong Lim, Gino Maa, Ken Mackenzie, Dan Nussbaum, and Donald Yeung, contributed to the Alewife machine in vast and varied ways. They wrote and rewrote software systems, simulators, and compilers until we possessed a first-class system; they designed everything from compiler primitives to hardware test jigs and power systems. It is a testament to the competence of the Alewife group as a whole that we booted the operating system and began executing code within days of receiving the first copies of the CMMU.

I will miss all of you and can only hope that I find a similarly dynamic group of students as I begin my career in academia.

The attribution of ideas in a project as large as Alewife is difficult at best. However, I would like to specifically thank David Chaiken, who was a major contributer to the architecture of Alewife.

I can only say that I miss our interactions — the two of us argued the CMMU into existence (sometimes rather loudly), and I would not have done it any other way. In a similar vein, Dan Nussbaum, my office-mate of many years, served as an priceless sounding board to weed out new and occasionally misdirected concepts for the Alewife system. David Kranz, our "master of all trades", provided continuity and backbone to our software efforts — from compilation, to operating systems, to device drivers, and back again. Finally, Ken Mackenzie was an important collaborator in the development of the UDM model of Chapter 2.

Anne McCarthy provided the wonderful cartoon illustrations that grace the major section headings. She also provided a level of support over the years that is without measure.

Finally, to my family who remained supportive during my long years in school: Thank you!

To the reader: The process of academic research is an exercise in revisionist-history — the act of cutting, pasting, and reframing the goals and motivations of a research project until it appears that participants possess supernatural levels of knowledge and insight. This document is, perhaps, no less misleading in that regard. In the following pages, I will speak about portions of the Alewife machine that were some of my central contributions; although I like to think that these contributions arose in orderly fashion, this belief is probably optimistic on my part. I leave it to the reader to make his or her own judgment.

Since large systems such as Alewife are the result of complex collaborations between many people, I will do my best to give credit where it is due. If I should fail to do so at someplace in this document, it is entirely unintentional and I offer my sincerest apologies in advance.

In the years that I worked on Alewife, I became somewhat attached to the project as a whole and the resulting prototype, warts and all. For good or bad, I touched upon all aspects of the project with my opinions and suggestions — always in search of improving the final result. Somewhat like a parent, I guess. Perhaps you can smile and nod as I tell you about Alewife.

# Contents

| Introd | oduction |                                                                     | 15 |

|--------|----------|---------------------------------------------------------------------|----|

| 1.1    | What a   | are "Message Passing" and "Shared Memory"?                          | 18 |

| 1.2    |          | Integrate Communication Semantics?                                  | 19 |

| 1.3    | Why I    | Integrate Communication Mechanisms?                                 | 22 |

| 1.4    |          | enges To Integration                                                | 28 |

| 1.5    |          | lewife Prototype                                                    | 32 |

| 1.6    | Overv    | iew of Results                                                      | 33 |

| 1.7    | Overv    | iew of Thesis                                                       | 34 |

| Part 1 | : Desi   | gn                                                                  | 35 |

| Chapte | r 2: Th  | ne User-Level Access Problem                                        | 39 |

| 2.1    | Interfa  | ace as an Extension to the ISA                                      | 41 |

| 2.2    | Feathe   | erweight Threads                                                    | 42 |

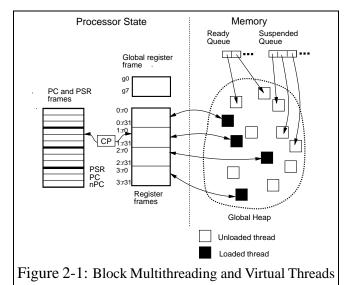

|        | 2.2.1    | Block Multithreading                                                | 42 |

|        | 2.2.2    | Scheduling for Featherweight Threads                                | 43 |

| 2.3    | Latenc   | cy-Tolerant Shared Memory                                           | 43 |

|        | 2.3.1    | Memory Model and Synchronization                                    | 45 |

|        | 2.3.2    | Latency Tolerance                                                   | 46 |

|        | 2.3.3    | Memory Fairness                                                     | 48 |

|        | 2.3.4    | Shared-Memory Implementation and LimitLESS Cache Coherence .        | 49 |

| 2.4    | User-I   | Direct Messaging                                                    | 50 |

|        | 2.4.1    | User-Direct Messaging Model                                         | 51 |

|        | 2.4.2    | User-Direct Messaging Interfaces                                    | 55 |

|        | 2.4.3    | Message Injection Interface                                         | 57 |

|        | 2.4.4    | Message Extraction Interface                                        | 63 |

|        | 2.4.5    | The User-Level Atomicity Mechanism                                  | 68 |

|        | 2.4.6    | Putting it all together: hardware support for user-level interrupts | 75 |

|        | 2.4.7    | User-Direct Messaging in a Multiuser System                         | 75 |

| 2.5    | The In   | nteraction Between Communication Models                             | 77 |

|        | 2.5.1    | The DMA Coherence Problem                                           | 78 |

|        | 2.5.2    | Message Atomicity and Shared-Memory Access                          | 80 |

| 2.6    | Postsc   | ript                                                                | 82 |

| Chapter | 3: Th   | e Service-Interleaving Problem                                   | 83  |

|---------|---------|------------------------------------------------------------------|-----|

| 3.1     | The Re  | fused-Service Deadlock                                           | 84  |

|         | 3.1.1   | Blocking Memory Operations Cause Deadlock                        | 85  |

|         | 3.1.2   | High-Availability Interrupts                                     | 85  |

|         | 3.1.3   | Interrupt Promotion Heuristics                                   | 87  |

| 3.2     | The Wi  | indow of Vulnerability Livelock                                  | 87  |

|         | 3.2.1   | Multi-phase Memory Transactions                                  | 88  |

|         | 3.2.2   | Processor-Side Forward Progress                                  | 89  |

|         | 3.2.3   | Four Window of Vulnerability Livelock Scenarios                  | 91  |

|         | 3.2.4   | Severity of the Window of Vulnerability                          | 94  |

|         | 3.2.5   | Closing the Window: Preliminaries                                | 96  |

|         | 3.2.6   | The Associative Locking Solution                                 | 97  |

|         | 3.2.7   | The Thrashwait Solution                                          | 100 |

|         | 3.2.8   | The Associative Thrashlock Solution                              | 104 |

| 3.3     | The Se  | rver-Interlock Problem                                           | 106 |

|         | 3.3.1   | Queuing Requests for an Interlocked Server                       | 107 |

|         | 3.3.2   | Negative Acknowledgment and the Multiple-Writer Livelock         | 108 |

| 3.4     | Protoco | ol Reordering Sensitivities                                      | 109 |

|         | 3.4.1   | Achieving Insensitivity to Network Reordering                    | 110 |

|         | 3.4.2   | Achieving a Clean Handoff from Hardware to Software              | 113 |

| 3.5     | Postscr | ript: The Transaction Buffer Framework                           | 116 |

| Chapter | 4: Th   | e Protocol Deadlock Problem                                      | 119 |

| 4.1     |         | Coherence Protocols and Deadlock                                 | 120 |

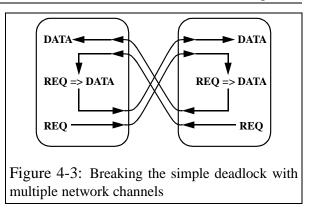

|         | 4.1.1   | Breaking Cycles With Logical Channels                            | 121 |

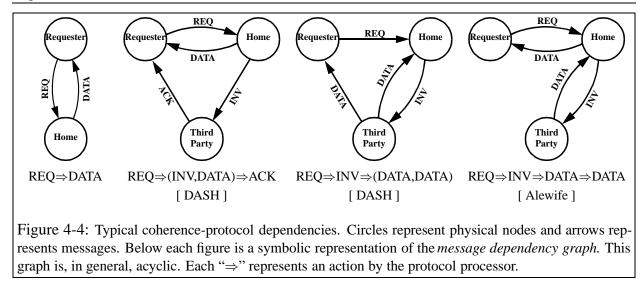

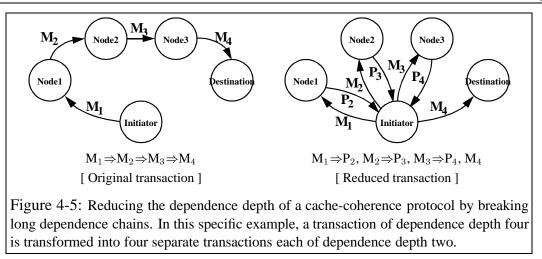

|         | 4.1.2   | Reducing the Dependence Depth                                    | 123 |

|         | 4.1.3   | Complexity of Deadlock Avoidance                                 | 124 |

| 4.2     | Messag  | ge Passing and Deadlock                                          | 125 |

|         | 4.2.1   | Elimination of Deadlock by Design                                | 126 |

|         | 4.2.2   | Atomicity is the Root of All Deadlock                            | 126 |

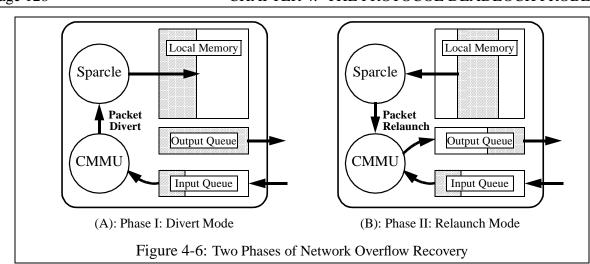

| 4.3     | Exploit | ting Two-Case Delivery for Deadlock Removal                      | 127 |

|         | 4.3.1   | Revisiting the Assumption of Finite Buffering                    | 127 |

|         | 4.3.2   | Detecting the Need for Buffering: Atomicity Congestion Events    | 130 |

|         | 4.3.3   | Detecting Queue-Level Deadlock                                   | 132 |

|         | 4.3.4   | Software Constraints Imposed by Queue-Level Deadlock Detection . | 133 |

|         | 4.3.5   | User-Level Atomicity and Two-Case Delivery                       | 135 |

|         | 4.3.6   | Virtual Queueing and Second-Case Delivery                        | 137 |

|         | 4.3.7   | What are the Hidden Costs of Two-Case Delivery?                  | 138 |

| 4.4     | Postscr | ipt: Two-Case Delivery as a Universal Solution                   | 143 |

| CONTENTS |                      |                                                               | Page 9 |

|----------|----------------------|---------------------------------------------------------------|--------|

| Part 2:  | Part 2: Consequences |                                                               | 145    |

| Chapter  | 5: Th                | ne Hardware Architecture of Alewife                           | 149    |

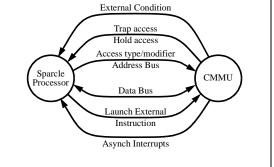

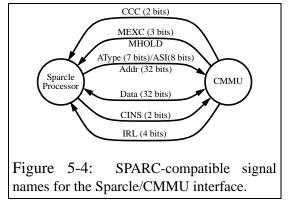

| 5.1      | Sparcl               | e Architecture and Implementation                             | 151    |

|          | 5.1.1                | Sparcle/CMMU Interfaces                                       | 151    |

|          | 5.1.2                | Support for Rapid Context-Switching and Featherweight Threads | 156    |

| 5.2      | The C                | ommunications and Memory Management Unit                      | 159    |

|          | 5.2.1                | The Division of Labor and the Network Topology                | 160    |

|          | 5.2.2                | The Sparcle/CMMU Interface Revisited                          | 163    |

|          | 5.2.3                | The Transaction Buffer Framework                              | 166    |

|          | 5.2.4                | Service Coupling and Memory Scheduling                        | 180    |

|          | 5.2.5                | Implementation of Local DMA Coherence                         | 185    |

| 5.3      | Mecha                | anics of the Alewife Implementation                           | 187    |

|          | 5.3.1                | Implementation of the Alewife CMMU                            | 187    |

|          | 5.3.2                | Validation Through Multi-Level Simulation                     | 190    |

|          | 5.3.3                | Hardware Test Methodology                                     | 192    |

| 5.4      | Postsc               | ript: Implementation is Possible and Necessary                | 193    |

| Chapter  | 6: Th                | ne Performance of the Alewife Prototype                       | 195    |

| 6.1      | Micro                | benchmarks and the Alewife Prototype                          | 197    |

|          | 6.1.1                | Performance of the Network                                    | 197    |

|          | 6.1.2                | Performance of Shared Memory                                  | 198    |

|          | 6.1.3                | Performance of Message Passing                                | 200    |

| 6.2      | Macro                | benchmarks and the Alewife Prototype                          | 203    |

|          | 6.2.1                | Performance of Shared-Memory Programs                         | 203    |

|          | 6.2.2                | Performance of Message-Passing Programs                       | 204    |

|          | 6.2.3                | Integration of Message Passing and Shared Memory              | 205    |

| 6.3      | How F                | Frequent IS Deadlock?                                         | 208    |

|          | 6.3.1                | Alewife: A Brief Case Study.                                  | 208    |

|          | 6.3.2                | The DeadSIM Simulator                                         | 209    |

|          | 6.3.3                | On the Character of Deadlocks                                 | 211    |

|          | 6.3.4                | The Deadlock-Free Interval with Alewife Parameters            | 214    |

|          | 6.3.5                | Deadlock Detection and the Importance of Hysteresis           | 215    |

|          | 6.3.6                | Future DeadSIM work                                           | 217    |

| Chapter  | 7: Al                | l Good Things                                                 | 219    |

| 7.1      | High-l               | Level Lessons of the Alewife Machine                          | 220    |

| 7.2      | How I                | Do the Lessons of Alewife Apply Today?                        | 223    |

| 7.3      |                      | d Work                                                        | 226    |

|          | 7.3.1                | Hardware Integration of Communication Models                  | 226    |

|          | 7.3.2                | Hardware Supported Shared-Memory                              | 227    |

|          | 7.3.3                | Message-Passing Communication                                 | 228    |

|          | 7.3.4                | Two-Case Delivery and Deadlock                                | 230    |

|          | 7.3.5                | Tradeoffs Between Communication Models                        | 230    |

| Page 10                               | ge 10 CONTI                    |     |

|---------------------------------------|--------------------------------|-----|

| Appendix A: Active Message Scheduling |                                | 233 |

| A.1                                   | Featherweight Threading        | 235 |

| A.2                                   | User-Level Atomicity Mechanism | 236 |

| Bibliography                          |                                | 237 |

| Index                                 |                                | 247 |

# **List of Figures**

| 1-1  | Anatomy of a Memory Reference.                                           | 23  |

|------|--------------------------------------------------------------------------|-----|

| 1-2  | Anatomy of a User-Direct Message.                                        | 25  |

| 1-3  | Integration of Communication Mechanisms in Alewife.                      | 27  |

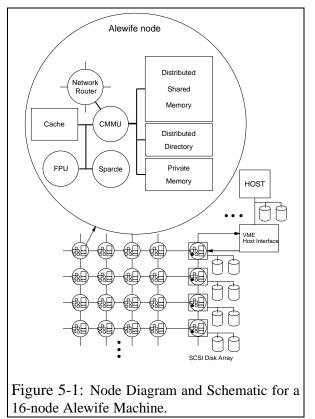

| 1-4  | Node Diagram and Schematic for a 16-node Alewife Machine.                | 32  |

| 2-1  | Block Multithreading and Virtual Threads                                 | 42  |

| 2-2  | Latency-Tolerant Shared-Memory Model/Interface.                          | 44  |

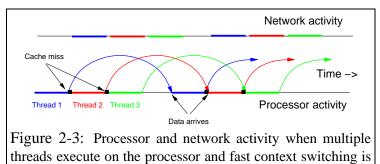

| 2-3  | Processor and network activity with fast context switching               | 47  |

| 2-4  | The User-Direct Messaging Model                                          | 52  |

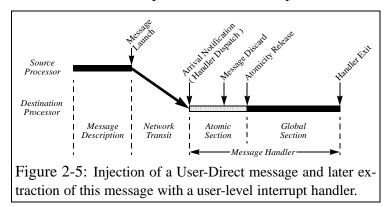

| 2-5  | Injection of a User-Direct message and later extraction via interrupts   | 54  |

| 2-6  | Instructions for the User-Direct Messaging interface                     | 56  |

| 2-7  | A uniform packet header format.                                          | 57  |

| 2-8  | Translation of a UDM send operation into UDM interface instructions      | 59  |

| 2-9  | Translation of a UDM sendc operation into UDM interface instructions     | 62  |

| 2-10 | Translation of a UDM receive operation into UDM interface instructions   | 64  |

|      | Translation of a UDM peek operation into UDM interface instructions      | 65  |

|      | Translation of UDM atomicity operations into UDM interface instructions  | 73  |

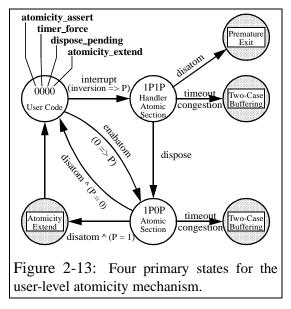

| 2-13 | Four primary states for the user-level atomicity mechanism               | 73  |

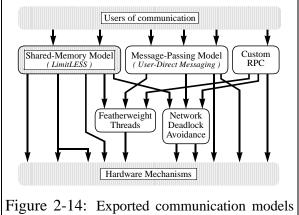

| 2-14 | Exported communication models in the Alewife multiprocessor.             | 82  |

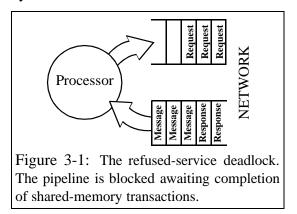

| 3-1  | The refused-service deadlock.                                            | 84  |

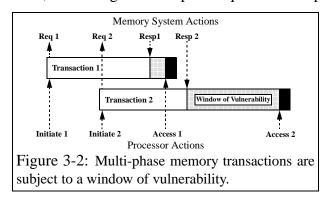

| 3-2  | Multi-phase memory transactions are subject to a window of vulnerability | 88  |

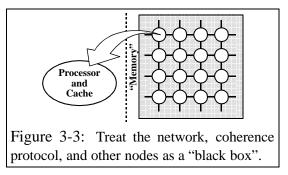

| 3-3  | View of memory system as a "black box."                                  | 89  |

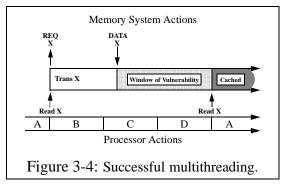

| 3-4  | Successful multithreading.                                               | 91  |

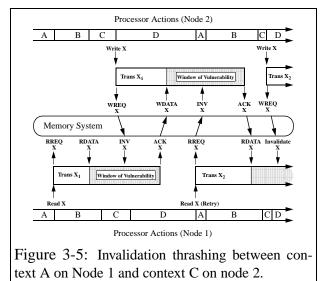

| 3-5  | An example of invalidation thrashing.                                    | 92  |

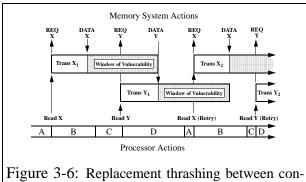

| 3-6  | An example of replacement thrashing.                                     | 92  |

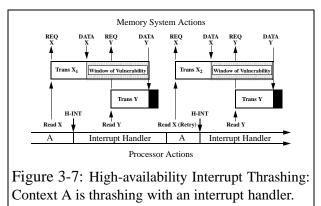

| 3-7  | An example of high-availability interrupt thrashing.                     | 93  |

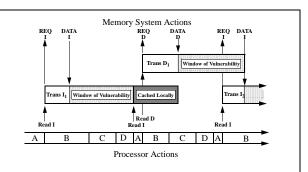

| 3-8  | An example of instruction/data thrashing.                                | 93  |

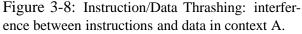

| 3-9  | Window of vulnerability: 64 processors, 4 contexts                       | 95  |

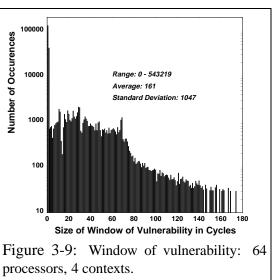

| 3-10 | Deadlocks that result from pure locking                                  | 98  |

| 3-11 | The Thrashwait Algorithm                                                 | 101 |

| 3-12 | Elimination of instruction-data thrashing through Thrashwait             | 103 |

| 3-13 | The effect of network reordering on an uncompensated protocol            | 110 |

| 3-14 | The Alewife coherence directory.                                         | 114 |

| 4-1  | Cache-coherence protocols contain cycles in their communication graphs   | 120 |

| 4-2  | Schematic representation for simple request/response deadlock            | 121 |

| Page 12 |  |

|---------|--|

|---------|--|

| 4-3        | Breaking the simple deadlock with multiple network channels                                                                          | 121        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4-4        | Typical coherence-protocol dependencies.                                                                                             | 122        |

| 4-5        | Reducing the dependence depth of a cache-coherence protocol                                                                          | 123        |

| 4-6        | Two Phases of Network Overflow Recovery                                                                                              | 128        |

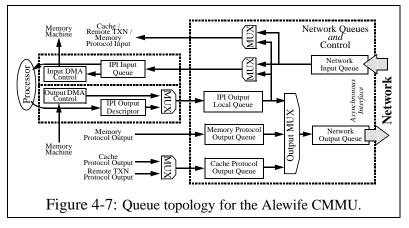

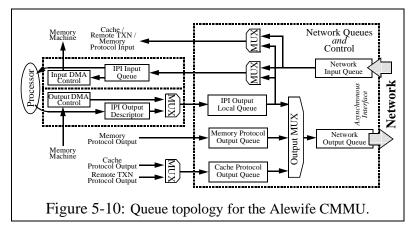

| 4-7        | Queue topology for the Alewife CMMU.                                                                                                 | 132        |

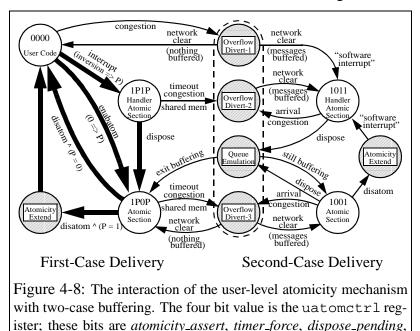

| 4-8        | The complete user-level atomicity state diagram.                                                                                     | 136        |

| <b>-</b> 1 |                                                                                                                                      | 1.40       |

| 5-1        | Node Diagram and Schematic for a 16-node Alewife Machine                                                                             | 149        |

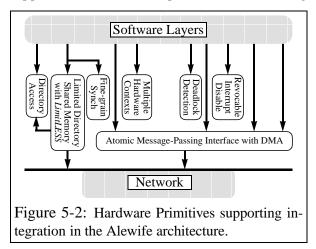

| 5-2<br>5-3 | Hardware Primitives supporting integration in the Alewife architecture.                                                              | 150        |

| 5-5<br>5-4 | High-level interface between the Sparcle pipeline and the CMMU                                                                       | 151<br>153 |

| 5-4<br>5-5 | Pipelining for arithmetic instructions.                                                                                              | 155        |

| 5-5<br>5-6 | Pipelining for a single-word load.                                                                                                   | 155        |

| 5-0<br>5-7 | Context switch trap code for Sparcle                                                                                                 | 155        |

| 5-7<br>5-8 | Breakdown of a 14-cycle context-switch on data for a load or store.                                                                  | 158        |

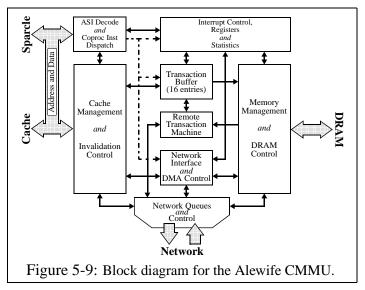

| 5-8<br>5-9 | Block diagram for the Alewife CMMU.                                                                                                  | 158        |

|            | Queue topology for the Alewife CMMU.                                                                                                 | 159        |

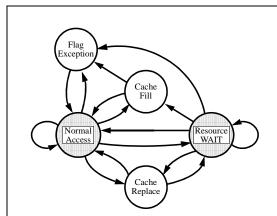

|            | A high-level view of the Cache Management Machine                                                                                    | 161        |

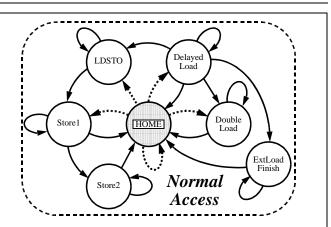

|            | 6                                                                                                                                    | 164<br>164 |

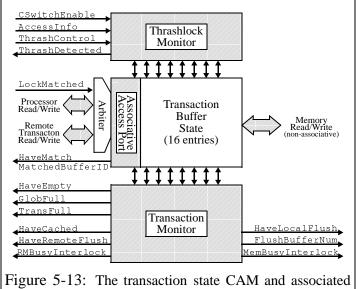

|            | An exploded view of the normal "state" of the Cache Management Machine The transaction state CAM and associated transaction monitors | 164        |

|            |                                                                                                                                      | 167        |

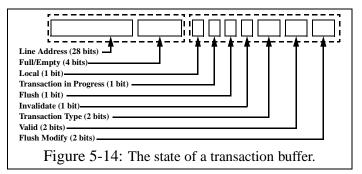

|            | The state of a transaction buffer                                                                                                    | 107        |

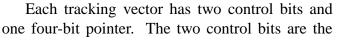

|            | Composition of the THRASHDETECTED signal                                                                                             | 175        |

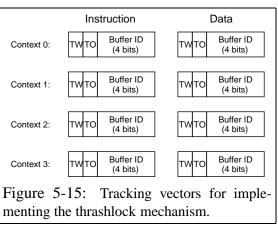

|            | Data Access with the ThrashLock Algorithm                                                                                            | 170        |

|            | Use of service coupling to maximize utilization of a contended resource.                                                             | 170        |

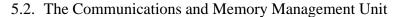

|            | Memory-side scheduling of a remote cache-coherence request.                                                                          | 180        |

|            | Memory-side scheduling of a local cache-coherence request.                                                                           | 183        |

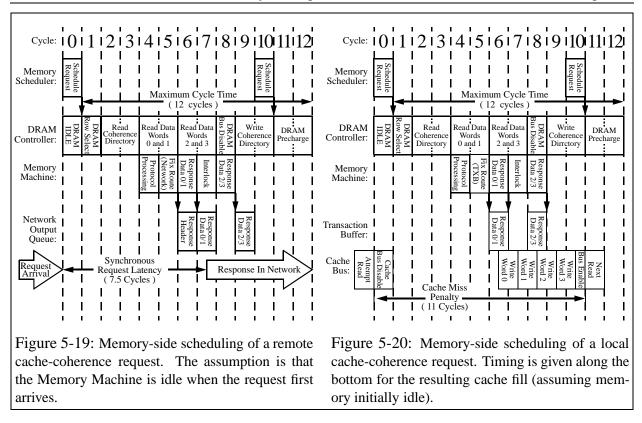

|            | The double-headed coherence queue that is used to implement local DMA coherence.                                                     | 185        |

|            | Floorplan for the Alewife CMMU ( $15$ mm $\times$ $15$ mm)                                                                           | 185        |

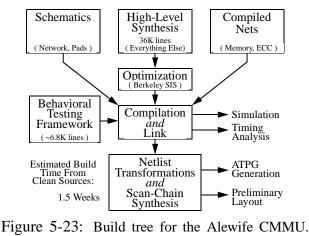

|            | Build tree for the Alewife CMMU                                                                                                      | 187        |

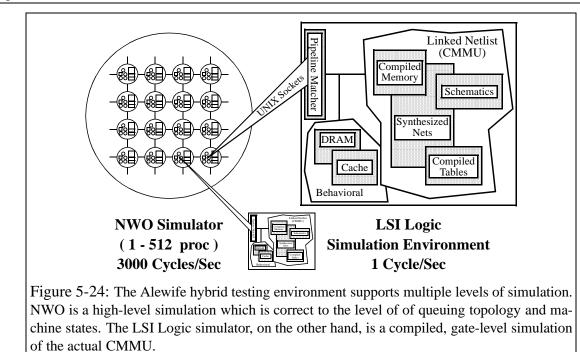

|            | The Alewife hybrid testing environment.                                                                                              | 189        |

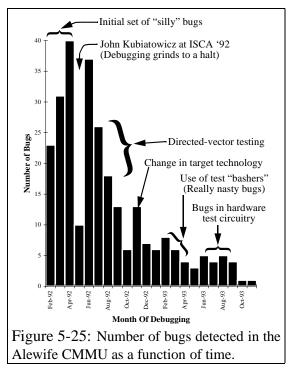

|            | Number of bugs detected in the Alewife CMMU as a function of time.                                                                   | 190<br>191 |

| 5-25       | Number of bugs detected in the Alewite CMINIC as a function of time                                                                  | 171        |

| 6-1        | 16-node machine and 128-node chassis populated with a 32-node machine                                                                | 195        |

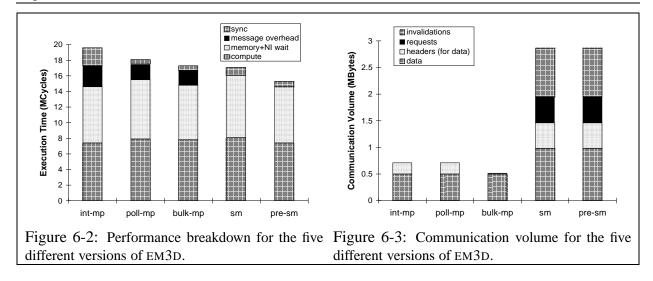

| 6-2        | Performance breakdown for the five different versions of EM3D.                                                                       | 206        |

| 6-3        | Communication volume for the five different versions of EM3D.                                                                        | 206        |

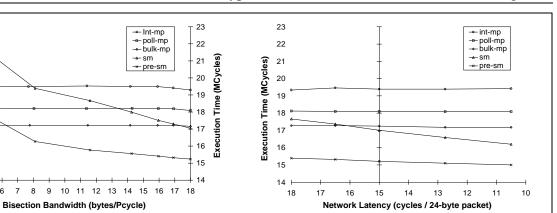

| 6-4        | Variation in performance of EM3D as function of bandwidth.                                                                           | 207        |

| 6-5        | Variation in performance of EM3D as function of latency.                                                                             | 207        |

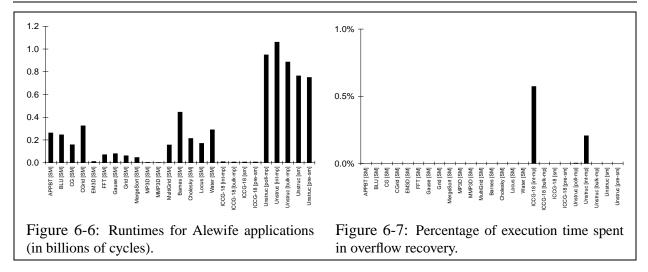

| 6-6        | Runtimes for Alewife applications (in billions of cycles).                                                                           | 209        |

| 6-7        | Percentage of execution time spent in overflow recovery.                                                                             | 209        |

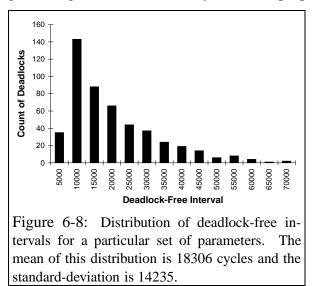

| 6-8        | Distribution of deadlock-free intervals.                                                                                             | 212        |

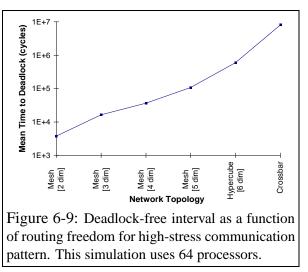

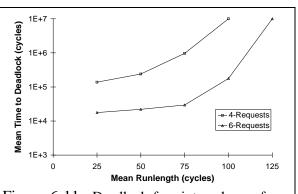

| 6-9        | Deadlock-free interval as a function of routing freedom                                                                              | 213        |

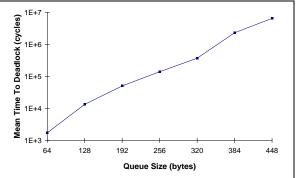

|            | Deadlock-free interval as a function of network queue size                                                                           | 213        |

|            | Deadlock-free interval as a function of run-length.                                                                                  | 215        |

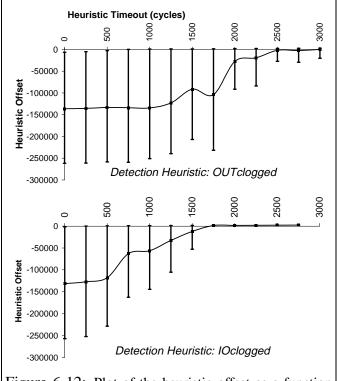

| 6-12       | Plot of the heuristic offset as a function of heuristic timeout value                                                                | 216        |

| A-1        | Scheduler code for user-level active message interrupts on the A-1001 CMMU                                                           | 234        |

|            |                                                                                                                                      |            |

\_\_\_\_\_

# **List of Tables**

| 2-1 | Examples of Alewife synchronizing loads and stores.                | 45  |

|-----|--------------------------------------------------------------------|-----|

| 2-2 | Interrupts and Exceptions for User-Direct Messaging interface.     | 57  |

| 2-3 | Control registers for User-Direct Messaging interface.             | 57  |

| 2-4 | Control bits for the user-level atomicity mechanism                | 70  |

| 3-1 | Window of Vulnerability Closure Techniques                         | 96  |

| 3-2 | Properties of window of vulnerability closure techniques           | 97  |

| 3-3 | The four meta-states of the Alewife coherence directory.           | 114 |

| 5-1 | Valid transaction buffer states.                                   | 169 |

| 5-2 | Functional block sizes (in gates) for the Alewife CMMU             | 187 |

| 5-3 | Module sizing for the message-passing portions of the Alewife CMMU | 188 |

| 6-1 | Three critical network parameters                                  | 197 |

| 6-2 | Typical nearest-neighbor cache-miss penalties at 20MHz             | 198 |

| 6-3 | Rough breakdown of a 38-cycle clean read-miss to neighboring node. | 199 |

| 6-4 | Overheads for message send and receive of a null active message    | 201 |

| 6-5 | Performance of shared-memory applications on Alewife.              | 204 |

Early multiprocessor research was divided into two separate camps based on *hardware communication primitives*: those advocating *shared memory* and those advocating *message passing*. Supporters of shared memory pointed to the fact that a shared-address space programming model is easy to reason about; its location-independent communication semantics frees programmers from the burden of explicitly locating shared data and from orchestrating interprocessor communication. For performance, they argued, shared-memory should be implemented directly in hardware. Supporters of message passing, on the other hand, maintained that shared-memory hardware was unscalable and difficult to build; message-passing is much simpler to implement, they argued, and provides a "minimum" communication primitive upon which other communication models (including shared memory) can be constructed. In this early state of affairs, researchers adhered religiously to one or the other of the research camps, often ignoring the fact that each approach has advantages and disadvantages.

Breaking with this tradition, the following thesis argues that an *integration* of shared memory and message passing is desirable from both architectural and implementation standpoints. Since shared-memory and message-passing *communication models* have different applications domains in which they are ideally suited, a system that integrates them can exploit the advantages of each. Further, such an integrated system can be efficiently *implemented* by combining primitive shared-memory and message-passing hardware mechanisms with a thin veneer of runtime software.

At another level, the architecture community has long struggled with the degree to which multiprocessor mechanisms should be integrated with memory and processor components. Proponents of least-effort "commodity parts" design methodologies attempt to bootstrap their multiprocessor design efforts by combining off-the-shell processor and memory components with a minimum of network coupling hardware. However, this does not necessarily represent the best implementation strategy. Low-latency, high-throughput access to data storage is of fundamental importance in uniprocessor systems, as demonstrated by the degree of engineering that is typically expended on uniprocessor memory systems design. *The memory system is no less important within a multiprocessor*. Further, well-designed uniprocessor memory systems share many features with multiprocessor memory systems: they are split phase and highly pipelined; they effectively process streams of requests from other levels of the memory system and respond with data. Thus, to exploit the similarity between uniprocessor and multiprocessor memory systems, this thesis argues for a tight integration of network and memory control, where integration here refers to single-chip integration.

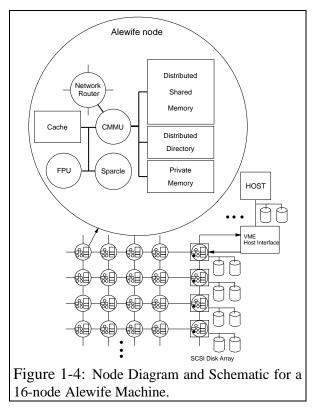

In short, this thesis is *about* integration at many levels of a multiprocessor system: communications models, operating-systems, hardware. Themes of integration will arise time and time again, but will be moderated by concerns of practicality – avoiding capricious or excessive implementation skirmishes in favor of carefully chosen battles. The ultimate test of a system design is, of course, a working system. In this thesis, the vehicle for exploring integration and the embodiment of the ideas contained herein is the Alewife multiprocessor. Alewife integrates cache-coherent shared-memory and user-level message passing, employs a scalable cache-coherence scheme, and functions with a single, bidirectional network channel. Its implementation exhibits a constant pernode hardware cost in the form of a handful of VLSI chips, including the Sparcle processor and the Alewife *Communications and Memory Management Unit*(CMMU). The CMMU provides fast, efficient communication mechanisms and can directly support machine-sizes up to 512 nodes. From the standpoint of the rest of this thesis, however, the most important feature of the Alewife machine is that it *exists* and is being used by a number of researchers. A 32-node machine has been operational since June of 1994.

### 1.1 What are "Message Passing" and "Shared Memory"?

In motivating the integration of message passing and shared memory, it is first important to understand what we mean by these terms. In fact, these terms may be interpreted at two different levels of abstraction, that of *communications model* and that of *hardware mechanism*.

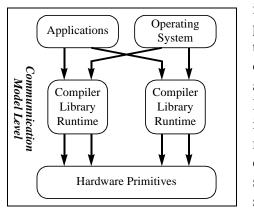

**Communications Models:** At the highest level of abstraction, the terms "shared memory" and "message passing" refer to communications models or paradigms that are directly interpreted by applications or systems programmers. The semantics of a given communications model can be thought of as a contract between the programmer and the underlying system, describ-

ing the behavior and guarantees that a programmer can expect, assuming that they fulfill their side of the bargain. In this context, the collection of semantics for shared memory are often referred to as the *memory model*; the pros and cons of various memory models form a large body of literature[1, 10, 41, 38]. The semantics of message passing paradigms have also been explored to some extent, but many of these models have deficiencies of one sort or another. In fact, in searching for a set of message passing semantics that are compatible with shared memory, we will spend a fair amount of time defining the *User-Direct Mes*-

*saging* model in later parts of this thesis. Note that support for a complete communications model is provided by the system as a whole: an amalgam of hardware, runtime systems, libraries, and compiler software that synthesizes the model as presented to the programmer. The figure to the left shows this concept and serves to highlight the fact that some layers of software, namely those that are used to *implement* communication models, must operate outside the guarantees and semantics of any one model. Instead, this software makes use of raw hardware mechanisms that may present incomplete guarantees or partial communication functionality.

For the purpose of the current discussion, we will content ourselves with a brief summary of the predominant features of shared memory and message passing. We will elaborate on these in later portions of the thesis.

SHARED MEMORY: One fundamental feature of shared memory that all communication is *implicit*, via loads and stores to a global address space. The physical location of data is completely unspecified by the model, except in so far as some data may be considered more expensive to access than other data. To communicate information, the processor issues load and store operations; the underlying system is responsible for deciding whether or not data is cached and for locating data in the event that it is not cached. A second important feature of shared MESSAGE PASSING: In contrast, message passing is an *explicit* communication model; all communication consists of explicit messages from processors that have data to those that need data. Any communication between processors must be accomplished by such messages. Further the arrival of a message at a destination processor constitutes an asynchronous event, since software must be invoked to handle messages. Consequently, synchronization and communication are unified with message passing; the generation of remote, asynchronous events is an integral part of any message-passing communication model.

These two characterizations of shared memory and message passing will be sufficient for the upcoming discussion of the advantages of integration.

**Hardware Mechanisms:** Having defined what the terms "shared memory" and "message passing" mean in the context of communication models, we would now like to turn to another usage of these terms, to refer to individual hardware mechanisms. In this context, "shared memory" and "message passing" refer to these individual hardware mechanisms that have the "look-andfeel" of message passing or shared memory, but that may not provide all of the facilities of a complete communications model. Thus, a shared-memory hardware mechanism would likely support a load-store interface that handles the common case aspect of global access to cached data directly in hardware. Other aspects of global access, such as the location of data during a cachemiss or the tracking of widely shared data items might require software intervention. Similarly, a message-passing hardware mechanism might provide hardware facilities for launching and consuming messages, but might not provide guarantees of deadlock freedom or atomicity without software support.

## **1.2 Why Integrate Communication Semantics?**

Given the clarifications of the previous section, we can restate one of our primary goals: this thesis will argue that an integration of message passing and shared memory is important *both* from the standpoint of communications model *and* hardware implementation. Before continuing this discussion, it is important to note that shared memory and message passing communication models are universal: each can be employed to simulate the other<sup>1</sup>. Thus the advantages to be attained via integration are not of the variety typically extolled by theorists: they have to do with slippery concepts such as communication overhead, implementation efficiency, and ease of programming.

Although the integration of shared memory and message passing has recently become a hot topic in the research community, this research has not made a clear distinction between the integration of communication models and implementation mechanisms. In an attempt to correct

<sup>&</sup>lt;sup>1</sup>However, it is much easier to simulated shared memory with message passing than the converse. The primary difficulty involves simulating the asynchronous event semantics of message passing with the polling semantics of shared memory.

this situation, we first talk about the intrinsic advantages and disadvantages of each of the communication models. In a subsequent section, we will consider reasons for integrating hardware communication mechanisms.

Advantages of the Shared Memory Model: Conventional wisdom in the multiprocessor research community is that it is important to support a *shared-address space* or *shared-memory* communication model. One of the primary reasons for this is that shared memory shelters programmers from the details of interprocessor communication: the location-independent semantics of shared memory allow programmers to focus on issues of parallelism and correctness while completely ignoring issues of where data is and how to access it. This can allow the "quick construction" of algorithms that communicate implicitly through data structures. In some sense, the shared-memory communication model offers one of the simplest extensions of the uniprocessor programming paradigm to multiprocessors.

Further, because shared-memory semantics are independent of physical location, they are amenable to dynamic optimization by an underlying runtime or operating system. In particular, techniques such as caching, data migration, and data replication may be employed transparently to enhance locality and thus reduce latency of access. This is extremely powerful, because it means that data layout can be dynamically adjusted toward optimal, even though the programmer ignores it. As with any online algorithm, of course, the dynamic reordering mechanisms of the underlying system are unlikely to achieve a global optimum in data placement given an arbitrarily naive initial placement. In this sense, the implicit nature of the shared-memory programming model is both its principal strength and weakness: since placement *is* implicit, the programmer is not required to help with the data placement process (advantageous), leaving the underlying system the onerous task of extracting an ideal data placement given only a memory reference stream (unfortunate).

Note that this complete absence of information flow from application to underlying system is not inherent in the shared-memory model. For instance, when sufficient parallelism is identified by the programmer or compiler, then rapid context-switching can be employed to overlap latency. Similarly, latency tolerance can also be achieved when the compiler identifies access patterns in advance and inserts non-binding prefetch operations into the instruction stream. Both of these latency tolerance techniques can dynamically adjust for poor or non-ideal data placement. Further, as will be discussed in a moment, there is a lot of potential for the compiler to assist in choosing a good initial data placement as well as in choosing timely points for data migration. In fact, static analysis can occasionally eliminate the need for general cache-coherence, permitting the use of more efficient communication mechanisms such as message-passing. All of these techniques aid in the *implementation* of the shared-memory communication model, maintaining the same location-independent semantics for the programmer.

**Disadvantages of Shared Memory:** One of the deficiencies of the shared-memory communication model is the fact that it is, by nature, a polling interface. While this can make for extremely efficient communication under some circumstances, it can have a negative impact on synchronization operations. This has been enough of a concern that many multiprocessor architects have augmented the basic shared-memory communication model with additional synchronization mechanisms. Another disadvantage of shared memory is that every "real" communication operation (*i.e.*  one that causes data to cross the network) requires a complete network round-trip; no one-way communication of data is possible.

Advantages of the Message Passing Model: One of the biggest semantic advantages of the message-passing communication model is the fact that it is, by nature, interrupt driven. Messages combine both data and synchronization in a single unit. Furthermore, the efficiency of this combination can easily be maintained by simple implementations – we shall see this in later chapters of this thesis. In this section, we want to distinguish those applications of message passing that are natural from a programmers perspective from those that represent the result of automatic code generation in support of other communication models, *e.g.* shared memory.

Message passing provides an "interrupt-with-data", that is desirable for a number of *operating systems* activities in which communication patterns are explicitly known in advance: I/O, scheduling, task and data migration, and interprocessor interrupts. Further, manipulation of large data structures such as memory pages is ideally mediated with a messaging communications model, both because bulk transfer (DMA) is a natural adjunct to message passing (send a well-defined block of data from here to there) and because messaging operates "outside" of the shared-memory mechanisms that are being handled. This latter property is important when manipulating the data structures that shared memory depends on, such as global page mappings. Note that, although message passing requires explicit management of data locality and communication, this is not a disadvantage in an operating system, since most operating systems explicitly manage their own data structures anyway.

In addition to operating systems functions, certain applications are amenable to a messagepassing communication model. Such applications have a large synchronization component and are typically referred to as "data-driven". Examples include event-driven simulation and solution of systems of sparse matrices by substitution. Also included in this category are programs written with *Active Messages*[113, 81], to the extent that Active Messages represents a desirable source-level communication model rather than a compilation target. In addition, message passing communication models are natural for client-server style decomposition, especially when communication must occur across protection domains. Note that the last decade has seen the emergence of a number of message-passing interfaces that support various polling semantics, such as *CMMD*, p4, and *MPI*. It is this author's belief, however, that these interfaces have arisen largely in reaction to the lack of good compilation and runtime-systems technology; they represent systems that grant users the ability (and corresponding need) for explicit management and tuning of communication<sup>2</sup>.

**Disadvantages of Message Passing:** In addition to requiring the explicit management of data and communication, the message passing paradigm has one intrinsic disadvantage that can be mitigated but not eliminated by good interface design: the presence of higher endpoint costs in message passing models as compared to shared memory. The cost of assembling and disassembling messages, often called *marshaling cost*, is intrinsic to message passing because messages are, by

<sup>&</sup>lt;sup>2</sup>One advantage to message passing that is being explicitly rejected here is the statement that it permits the easy porting of "dusty-deck" applications that have been written with message-passing interfaces.

nature, transient and unassociated with computational data structures. At the source of a message, data is gathered together from memory based data structures and copied into the network. At the destination, the reverse must occur, namely data must be copied from the network into memory based data structures. This is an intrinsic cost of message passing and may be contrasted with shared memory, for which data remains associated with memory-based data structures at all times, even during communication.

It is important to note, however, that the marshaling cost of message passing can be less of an issue in comparison with shared memory when *implementation* and *communication patterns* are taken into consideration. For instance, communication patterns that exhibit poor cache locality and multiple round-trip network latencies can strongly degrade the performance of hardware-based shared-memory mechanisms. Further, certain classes of communication require copying anyway; page migration is a good example of this. In such cases, the marshaling cost in message passing is directly matched by copying costs in shared memory.

**Combined Semantics:** One obvious conclusion from the above discussion is that the sharedmemory and message-passing communication models each have applications domains to which they are ideally suited. In fact, a mixture of the two may even be appropriate within different phases of a *single* application. A corollary to this conclusion is that *it is desirable for general purpose multiprocessors to support* both *communication models, and to do so efficiently*. Interestingly enough, this conclusion has not been uniformly embraced by multiprocessor architects or the research community. However, even skeptics should agree that this conclusion seems inevitable given the fact that shared memory is universally viewed as advantageous for applications writers, while the advantages of message passing to operating systems design is manifest and continues to be noted by systems architects. This author, however, maintains something stronger: integration is important at the applications level. This conclusion will become even clearer when we look at the way in which communication models at one level (say applications source) are implemented by mechanisms at lower levels (compilers, runtime system, and hardware).

### **1.3 Why Integrate Communication Mechanisms?**

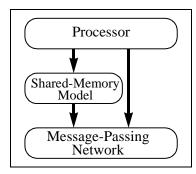

In the previous section we concluded that a multiprocessor system should provide both sharedmemory and message-passing communication models. With this goal in mind, the question then

becomes one of how to best implement such a multiprocessor. An extended answer to this question is, in fact, one of the primary topics of this thesis. A more simplistic answer to this question, however, is that we should provide a mixture of both shared-memory and message-passing communication mechanisms in hardware[58]. There are two reasons for this integration. The first, illustrated to the left, is one of opportunity: in striving for scalable performance, multiprocessor architects have abandoned buses in favor of generalized packet-switched networks to carry information between pro-

cessors. As a consequence, the lowest level of communication (i.e. the physical transport layer)

carries messages, *even in a shared-memory multiprocessor*. By itself, this observation would seem to indicate that the most prudent course of implementation would be to provide message passing support directly in hardware and to emulate shared memory in software. However, this proposal leads us to the second reason for employing an integration of mechanisms: the fact that the shared-memory and message-passing communication models have sufficiently different properties that it is expensive to implement one entirely with the other. Let us expand on this further.

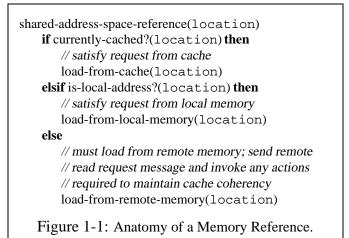

Anatomy of a Shared-Memory Reference: One of the primary virtues of the shared-memory communication model is its location independence. Such independence comes at a cost,

however, especially when coupled with caching. During the execution of an application written with a shared-memory communication model, the actions indicated by pseudo-code in Figure 1-1 must be taken for *every* reference to shared data. This pseudo-code represents the process of discovering *where* data actually resides (local cache, local node, or remote node) and *retrieving* the data once it has been located. We will call this process *locality resolution*. The first test in this figure is only necessary if local caching is allowed; however,

the second test is required for any implementation of a shared-memory communication model. Although locality resolution must occur for every shared reference, it may be performed at a variety of levels in the compiler, runtime system, or hardware<sup>3</sup>. Lets explore this a bit further.

For simplicity, assume that there are two types of shared-memory applications: *static* and *dynamic*. In static applications, the control flow of the program is essentially independent of the values of the data being manipulated. Many scientific programs fit into this category. Static applications have the virtue that some or all of the locality resolution code of Figure 1-1 can be performed by the compiler; no runtime overhead is incurred as a result. There has been a great deal of work in this area for scientific programs written in various dialects of FORTRAN and targeted at message-passing hardware [7, 19, 57, 74, 94, 121]. In dynamic applications, on the other hand, control flow is strongly dependent on the data being manipulated. Many symbolic applications fit into this category. Dynamic applications are not amenable to the same degree of compiler analysis as static applications; it is usually not possible to know *a priori* whether or not a particular reference will be to local or remote memory. Consequently, locality resolution must occur at runtime. Although most real programs will lie somewhere between these two extremes (by having some parts that are dynamic and others that are static), state-of-the-art compiler technology cannot yet reliably disambiguate communication styles<sup>4</sup>. As a result, most shared-memory applications end up performing locality resolution at runtime.

<sup>&</sup>lt;sup>3</sup>Although these actions could also be coded explicitly by the programmer, we exclude that as an option here because such coding would represent use of a message-passing communication model.

<sup>&</sup>lt;sup>4</sup>This is a situation that the author believes will continue to improve, however.

Hardware support for locality resolution is the essence of the distinction between sharedmemory and message-passing hardware architectures. In the former, the instruction to reference memory is the same whether the object referenced happens to be in local or remote memory; the local/remote checks are facilitated by hardware support to determine whether a location has been cached (cache tags and comparison logic) or, if not, whether it resides in local or remote memory (local/remote address resolution logic). If the data is remote and not cached, a message will be sent to a remote node to access the data. Because shared-memory hardware provides direct support for detecting non-local requests and for sending a message to fetch remote data, a single instruction can be used to access *any* shared-address space location, regardless of whether it is already cached, resident in local memory, or resident in remote memory. Assuming that local shared data access is handled at hardware speeds, this has the important consequence that access to shared data can be extremely rapid (*i.e.* of the same speed as an access to unshared data) when data is cached or resident on the local node. Thus, shared-memory hardware enables dynamic locality optimization through caching and data migration.

As argued above, the handling of local cache-misses to shared data in hardware is desirable from the standpoint of permitting transparent locality optimization through data migration. There is another way to consider this. To the extent that "real" communication must cross node boundaries and traverse the network, access of local shared data does not involve communication. As a result, the locality resolution that accompanies such access is an artifact of the shared-memory communication model. By placing locality resolution in hardware (including the fetching of local shared data during a cache miss), shared-memory architectures avoid penalizing accesses that would be handled entirely in hardware for hand-optimized message-passing programs. Further, as will be shown later in this thesis, the difference between handling local and remote shared data access in hardware is insignificant, especially for a restricted class of sharing patterns<sup>5</sup>. This, in turn, means that real communication through shared-memory can be extremely efficient, easily rivaling or surpassing that of hand-tuned message-passing programs on fine-grained message-passing architectures. The hardware handling of remote shared-memory accesses has a hidden advantage: no need for asynchronous interrupt handling or polling to service requests from remote nodes (at least not in the "common" case). This can be extremely important on machines that have expensive interrupt handling.

In contrast to shared-memory architectures, message-passing hardware architectures do not provide hardware support for either local/remote checks or caching<sup>6</sup>. Hence, they cannot use a single instruction to access locations in the shared-address space. In the most general case, they must implement the locality resolution code of Figure 1-1 entirely in software. This increases the cost of accessing shared-data, even if it is present on the local node. In addition, implementation of the general shared-memory communication model on a message-passing architecture incurs an additional cost, that of handling asynchronous requests for data from remote nodes. This, in turn, forces the use of frequent polling or interrupts in order to ensure that nodes make reasonable forward progress.

A simple conclusion here is that message-passing architectures are insufficient platforms for

<sup>&</sup>lt;sup>5</sup>*e.g.* handling limited read-sharing directly in hardware[23].

<sup>&</sup>lt;sup>6</sup>The J-machine[87] provides a hardware associative memory that served as a cache on object locations. This approach merely accelerates the local/remote check of Figure 1-1; it does not eliminate it.

the high-performance implementation of shared-memory communication models. In the past, it was deemed that these deficiencies were unavoidable, given the difficulty of building large-scale shared-memory multiprocessors. However, machines such as DASH [69, 70], Alewife[3] (the topic of this thesis), and others, have shown that the mechanisms required to build scalable shared-memory multiprocessors are not of unreasonable complexity.

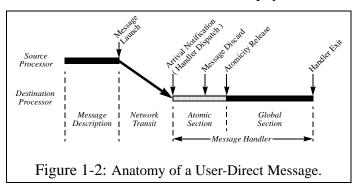

Anatomy of a Message Transaction. One advantage of the message-passing communication model is its integration of data and synchronization. Another is the direct nature of communication: data flows directly from source processor to destination processor, without unnecessary network crossings. One would hope that both of these properties would be directly retained by any implementation. Figure 1-2 illustrates the anatomy of a message communication in the context of the User-Direct Messaging model. This figure illustrates the four different phases of a message communication. The first of these, message description, involves describing the contents of the outgoing message to the communication layer; this is terminated by a message launch operation. The second, network transit, represents the time after the message is committed to the transport layer but before has been received. On reception, an interrupt is generated and a message handler is invoked as a result. The third phase of communication, the atomic section, is the period during which the message handler executes atomically with respect to other message handlers, *i.e.* with message interrupts disabled. Among other things, a handler must examine and free its message from the communication layer during the atomic section. The fourth and optional phase of message communication, termed the global section, allows the message handler to continue to execute as a first-class thread with interrupts enabled.

As shown in Figure 1-2, the message-passing communication model differs from shared memory in two important ways. First, it consumes minimal resources from the physical trans-

port layer, requiring no more than a single network traversal from source to destination. In contrast, typical shared-memory cache-coherence protocols can require up to *four* network traversals for the simple transaction illustrated by Figure 1-2. This may seem surprising until one considers the fact that these protocols make use of communication *heuristics* which are optimized for good average behavior over a

range of shared-memory communication patterns; consequently, they are unlikely to produce an optimum pattern of physical messages for all applications. Message-passing, on the other hand, provides access to the lowest-level primitives of the physical transport layer, thus permitting arbitrarily simple (or complex) communication patterns to be constructed, although at the cost of additional software overhead at the endpoints<sup>7</sup>.

The second important way in which message passing differs from shared memory is that mes-

<sup>&</sup>lt;sup>7</sup>Some researchers have attempted to acquire this same network efficiency by augmenting their cache-coherence protocols with *remote-write* capability, but this is not general and does not convey the synchronization advantages presented by a message-passing communication model.

sage passing involves an explicit interrupt model that permits users to receive message notification via interrupts. Such a user-level interrupt model requires an associated atomicity mechanism that permits users to disable interrupts without violating the integrity of the operating system; in Alewife, atomicity is provided by a *revocable interrupt disable* mechanism. Although we will discuss this mechanism later when we present User-Direct Messaging, the important point here is that atomicity is unnecessary for shared-memory communication models.

A third point that we advance here is the fact that typical shared-memory architectures do not provide support for large block transfers. Such transfers are desirable for a range of operations, from block I/O to data migration. Although support for block transfer can be included in a shared-memory architecture (in the form of hardware-accelerated memory-to-memory copy) this operation can be more efficiently accomplished via message-passing: the large quantity of data argues for efficiency at the transport level, *i.e.* direct transfer of data from source to destination (no extra network round-trips) via large network packets (reducing network routing overhead). Consequently, message-passing communication models ideally export DMA mechanisms which are not required for shared-memory.

Thus we have provided at least three reasons that a machine which provides only sharedmemory is not entirely suitable for message-passing communication models: transport efficiency, atomicity, and block transfer.

An Integration of Mechanisms. As a result, one answer to the question of why to integrate shared-memory and message-passing *mechanisms* is that no one set of mechanisms is sufficient to implement both share-memory and message-passing *communication models*. This answer we have examined in the previous pages.

The integration of mechanisms can have additional benefits, however, in that communication models can be implemented more efficiently than might otherwise be possible. For instance, the presence of integrated mechanisms enables compiler transformations which analyze source code written in one communication model to emit instructions in a more appropriate communication model. The earlier discussion of compiler-based locality resolution is one example of this – static applications written with a shared-memory communication model can be compiled to produce binaries which utilize the message-passing communication model at runtime; for certain classes of applications, this may actually result in the shortest possible runtime.

Another, more concrete example of the benefits of integration involves Alewife's sharedmemory communication model, called LimitLESS. The presence of hardware message-passing mechanisms relaxes the functionality required from the hardware shared-memory: these mechanisms can implement a restricted subset of the cache-coherence protocol[23] and can ignore the issues of protocol deadlock entirely[60]. We will explore these benefits in later portions of the thesis.

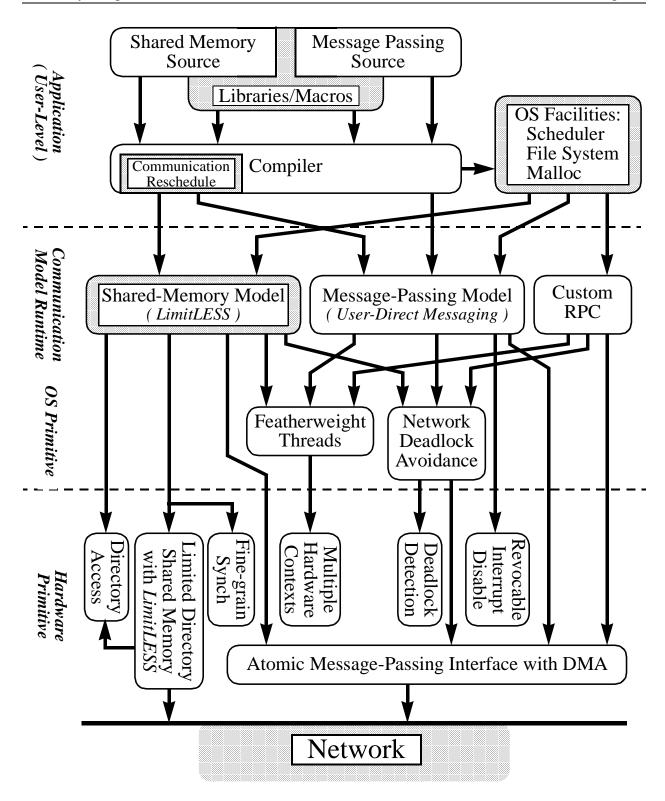

Figure 1-3 previews the various levels of hardware and software mechanisms present in the Alewife machine and forms a road map to the implementation portions of the thesis, since most of these mechanisms (as well as justification for this particular partitioning) will be described in detail later. For now, note that this figure shows four distinct levels of implementation, from the application level through to the hardware. Although the machine as a whole integrates both shared-memory and message-passing communication models, this diagram also highlights several

Figure 1-3: Integration of Communication Mechanisms in Alewife. Shaded boxes represent points at which Message Passing and Shared Memory are explicitly integrated.

point at which these models are entwined (shaded regions): special synchronization *libraries*[75] integrate both shared memory and message passing communication to exploit the best of each; the *compiler* attempts to extract an efficient mix of shared-memory and message-passing code from shared-memory source<sup>8</sup>; the LimitLESS cache coherence *model*[23, 24] explicitly integrates shared-memory and message-passing communication hardware mechanisms; finally, the *network* carries traffic for both shared-memory and message passing communication mechanisms.

## **1.4 Challenges To Integration**

Having identified that integrated architectures are both interesting and desirable, we now consider some of the issues that complicate the design and implementation of a such architectures. At the level of design, we identify three major challenges to integration:

- 1. The User-Level Access Problem

- 2. The Service-Interleaving Problem

- 3. The Protocol Deadlock Problem

These are listed in decreasing order of architectural abstraction (or, alternatively, in decreasing order of impact on the user). These three issues will arise during much of the *Design* portion of this thesis. We want to take a few moments at this time to define these challenges and provide a brief outline of their solutions.

**The User-Level Access Problem:** Loosely stated, the *User-Level Access Problem* involves a desire to export hardware communication mechanisms directly to user-level while maintaining a clear distinction between system and user. This desire is motivated by the fact that the greatest combined performance and flexibility can often be achieved when user-code can interact directly with hardware mechanisms, without the intervention of system-level software. It reflects a strong belief in the integrated-systems approach that was the hallmark of the RISC revolution, *i.e.* a careful blending of primitive hardware mechanisms with a thin layer of runtime software and optimizing compiler technology. We intend to adopt this philosophy in a machine with integrated message passing and shared memory. Thus, to be more precise, our definition the User-Level Access Problem for an integrated architecture involves the search for a simultaneous, optimal solution to the following three questions:

- 1. What are the *semantics* of the communication models?

- 2. How do these models *interact* with one another?

- 3. What *interfaces* should the user employ to access communication mechanisms?

Our search for a simultaneous answer to these questions may be contrasted with less-optimal approaches that (1) choose a set of communication semantics without regard for implementation

<sup>&</sup>lt;sup>8</sup>Note that this compiler is still in the early stages of exploration at this point.

complexity, or (2) which propose a set of hardware mechanisms without a well-defined user model, or (3) which construct hardware mechanisms without careful attention to interfaces.

One of the most desirable characteristics for a solution is that it achieves high performance without compromising protection or incurring unreasonable implementation complexity. Thus, we seek semantics that are just powerful enough to yield good and predictable performance – no more so. In guiding our search, we employ two rules of thumb:

- 1. View the set of hardware communication mechanisms as a "bag of tricks".

- 2. View communication interfaces as extending the instruction set architecture (ISA).

The first viewpoint states that communication operations that are used by the programmer are not directly reflected by hardware operations; rather, they are constructed by the compiler, library, or runtime system from a set of primitive hardware mechanisms ("bag of tricks"). This viewpoint is illustrated by Figure 1-3. It focuses attention on the construction of a minimal set of hardware mechanisms that satisfy our needs for correctness and performance. The second viewpoint advocates the direct export of hardware communication mechanisms to the user (via user-level instructions) while maintaining a clear distinction between the system and user. Philosophically, this approach reflects a view that communication is as fundamental as computation and should thus be reflected in the instruction set<sup>9</sup>. This viewpoint is not new (see, for instance, [116, 34, 14, 88, 89]); however, we seek an architecture which (1) integrates message passing and shared memory communication while (2) attempting to balance the performance of communication mechanisms against single thread performance and implementation complexity.

To briefly preview our result, the Alewife solution to the User-Level Access Problem embraces the following five hardware mechanisms:

- **1.** *Sequentially consistent* shared memory with extensions for prefetching, fine-grained synchronization, and rapid context-switching.

- 2. A *single-user model* of the network which provides direct, user-level access to hardware queues while remaining virtualized for resource sharing and protection. Included as part of this mechanism is a user-level DMA mechanisms with *locally coherent* semantics.

- **3.** *Multiple register sets* for fast thread creation, latency tolerance and rapid interrupt handling.

- **4.** A formalized notion of *atomicity* which provides low-overhead, user-level control of message interrupts without violating protection.

- 5. A mechanism for detecting deadlock in the network.

Each of these mechanisms appears at the bottom of Figure 1-3.

<sup>&</sup>lt;sup>9</sup>It should be noted that the process of adding user-level operations or instructions is often confused with the mechanism of interface/implementation. Consider, for instance, the progression of floating-point hardware from memorymapped "coprocessor" interfaces to highly-integrated multi-issue floating-point pipelines.

Of the two communication models, message passing presents the greatest challenge for fast interfaces and protection. The shared-memory interface is well-established and easily protected with standard uniprocessor techniques. Further, shared-memory buries much of the details of communication at a level which the user is unable to influence: cache-coherence messages are of fixed size and well-defined composition, are typically restricted in quantity, and are consumed immediately at their destinations. In contrast, message passing can involve messages of arbitrary size and composition, may permit the network to be flooded, and may expose the system to deadlock since the user may refuse to consume messages.

**The Service Interleaving Problem:** The *Service Interleaving Problem* in an integrated architecture arises from the presence of uncontrolled simultaneity in an multiprocessing environment. This simultaneity arises from several sources: First, by their very nature, multiprocessors support multiple instruction streams (at least one per node), each of which can generate shared-memory communication traffic. Second, latency-tolerance techniques such as prefetching and rapid-context switching serve to overlap communication by increasing the number of outstanding requests from each node. Third, message-passing interfaces give rise to a potentially unbounded number of outstanding requests from each node. Hence, the memory system and network must correctly support many simultaneous requests with arbitrary ordering between them. Further, the boundaries between shared memory and message passing can be explicitly crossed when hardware events are handled by software (such as for the LimitLESS coherence protocol); this can introduce simultaneity in which cache-coherence structures are access by both hardware and software.

Hence, the Service-Interleaving Problem requires order amidst this chaos. It can be stated as requiring two guarantees:

- 1. All communication operations must complete eventually.

- 2. All communication operations must complete correctly.

The first statement asserts that the system is free of both livelock and deadlock. It requires the solution of three problems, the *refused-service deadlock*, the *window of vulnerability livelock*, and the *server-interlock problem*<sup>10</sup>. The refused-service deadlock refers to a form of priority inversion in which an asynchronous interrupt is deferred pending completion of a dependent operation or in which one class of communication (such as messages) prevents the completion of another class of communication (such as messages) prevents the completion of another class of communication (such as shared memory). The window of vulnerability livelock arises naturally in systems with split-phase memory transactions, when requested data can return to a node and be invalidated before it is accessed. Finally, the server-interlock problem is a memory-side dual to the window of vulnerability livelock and arises naturally in cache-coherence protocols. Ignoring this problem can lead to deadlock, while partial solutions can introduce livelocks, both of which can prevent the forward-progress of memory operations.

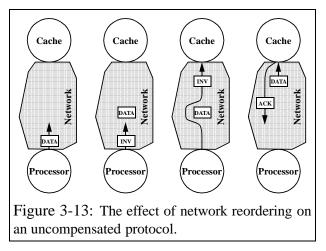

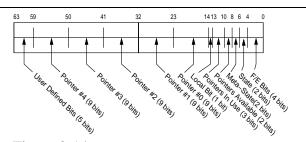

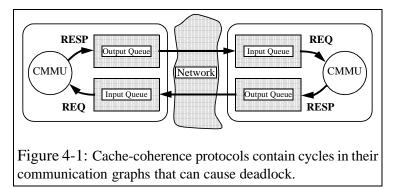

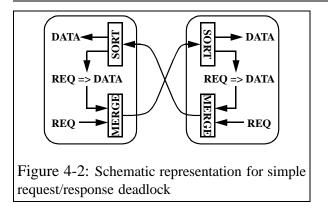

The second statement implies the existence of a cache-coherence protocol to maintain data consistency, and the presence of explicit mechanisms to deal with message and event reordering. Although all cache-coherence protocols deal explicitly with internode parallelism, such protocols