#### A Decompositional Approach to Computer System Performance Evaluation

Aaron B. Brown

TR-03-97

Center for Research in Computing Technology Harvard University Cambridge, Massachusetts

#### A Decompositional Approach to Computer System Performance Evaluation

A Thesis presented

by

Aaron Baeten Brown

to

Computer Science

in partial fulfillment of the honors requirements

for the degree of

Bachelor of Arts

Harvard College

Cambridge, Massachusetts

April 7, 1997

# Table of Contents

| 1 | Introduction                                                                     | 1  |

|---|----------------------------------------------------------------------------------|----|

| 2 | Decomposing the Performance of the Operating System Kernel                       | 9  |

|   | 2.1 Related Work: Benchmarking Operating Systems                                 | 11 |

|   | 2.2 Microbenchmark Tools: Revising Imbench into hbench-OS                        | 13 |

|   | 2.2.1 Timing Methodology                                                         | 15 |

|   | 2.2.2 Statistical Methodology                                                    | 17 |

|   | 2.2.3 Increased Parameterization                                                 | 18 |

|   | 2.2.4 Context Switch Latency                                                     | 18 |

|   | 2.2.5 Memory Bandwidths                                                          | 21 |

|   | 2.2.6 New Output Format                                                          | 22 |

|   | 2.3 Case Study: A Performance Decomposition for NetBSD on the Intel x86 Platform | 22 |

|   | 2.3.1 Bulk Data Transfer                                                         | 24 |

|   | 2.3.2 Process Creation                                                           | 36 |

|   | 2.3.3 Signal Handler Installation                                                | 39 |

|   | 2.4 Conclusions                                                                  | 41 |

| 3 | Extending the Performance Decomposition to User Applications                     | 43 |

|   | 3.1 Methodology                                                                  | 44 |

|   | 3.2 Case Study: Developing Tools                                                 | 46 |

|   | 3.3 Case Study: The Apache Web Server                                            | 49 |

|   | 3.3.1 Step 1: Decomposing Apache's Internal Structure                            | 49 |

|   | 3.3.2 Step 2: Connecting the Application and Operating System Hierarchies        | 51 |

|   | 3.4 Related Work: Understanding Application Performance                          | 54 |

|   | 3.5 Conclusions                                                                  | 56 |

| 4 | Distilling the Detail: Performance at the OS-Application Abstraction Boundary    | 57 |

|   | 4.1 Methodology                                                                  | 58 |

|   | 4.2 Analysis of Methodology and Potential Future Research Directions             | 63 |

|   | 4.3 Case Study: Predicting the Performance of the Apache Web Server              | 64 |

|   | 4.4 Related Work: Application Performance Characterization and Prediction        | 70 |

| 5 | Conclusion                                                                       | 72 |

| R | eferences                                                                        | 74 |

| A | cknowledgments                                                                   | 77 |

## Chapter 1

### Introduction

Throughout the history of computers, a primary design goal in all systems has been to achieve maximum performance. When digital computing was in its infancy, performance was measured in terms of throughput of scientific calculations: in the mid-1940s, the then-new ENIAC's most-touted design feature was its ability to calculate artillery trajectory tables over 1,000 times faster than earlier electromechanical computers [18]. Surprisingly, this traditional approach to performance evaluation and optimization remains in widespread use today. Admittedly, one does not see today's processor designers optimizing their commodity CPUs for use in anti-aircraft guns, but it is still true that the performance evaluation suites in widespread use are based either on models of scientific computation or on a systems programming or hardware design workload [23][24]. These models are becoming progressively less valid for today's applications: modern users are focusing more and more of their attentions on applications heavy with multimedia and networking content. One need not look farther than the explosive success of the world-wide web and the plethora of multimedia extensions and protocols that it has spawned to see this trend in action.

The demands that such modern applications make on the hardware and software subsystems that support them are very different than those simulated and evaluated by the traditional set of performance analysis tools. As modern applications become increasingly dependent on multimedia, graphics, and data movement, they are spending an increasing fraction of their execution time in the operating system (OS) kernel, an area of the system almost completely ignored by such traditional performance-evaluation tools. As an illustrative example, consider what must undoubtedly be today's leading server application: the web server. Web servers have been shown to spend over 85% of their CPU cycles running operating system code [4]; in contrast, the near-ubiquitous SPEC benchmarks execute less than 9% of their instructions in the OS kernel [7]. The figures in Table 1 show that the web server is not unique: the other typical multimedia, commercial, and GUI workloads listed similarly spend between 20% and 90% of their instructions in the ker-

|         | Benchmark   | User                                     | Kernel        | %-Kernel |  |

|---------|-------------|------------------------------------------|---------------|----------|--|

|         |             | Dynamic Instruction Counts (in millions) |               |          |  |

|         | compress    | 70.9                                     | 3.5           | 4.7      |  |

|         | espresso    | 332.3                                    | 6.2           | 1.8      |  |

| 292     | gcc         | 145.7                                    | 4.3           | 2.9      |  |

| SPEC92  | 022.li      | 121.4                                    | 4.6           | 3.7      |  |

|         | 072.sc      | 81.8                                     | 7.8           | 8.7      |  |

|         | 089.su2cor  | 385.2                                    | 2.2           | 0.1      |  |

|         | jpeg_play   | 138.9                                    | 12.2          | 8.1      |  |

| IBS     | mpeg_play   | 77.8                                     | 21.6          | 21.7     |  |

| IB      | verilog     | 36.4                                     | 10.6          | 22.6     |  |

|         | video_play  | 15.8                                     | 36.7          | 69.9     |  |

|         | TPC-A       | not available                            | not available | 40       |  |

|         | TPC-C       | not available                            | not available | 43       |  |

| Maynard | Netperf     | not available                            | not available | 97       |  |

| Mayı    | Laddis      | not available                            | not available | 100      |  |

|         | Kenbus      | not available                            | not available | 23       |  |

|         | Sdet        | not available                            | not available | 50       |  |

|         | Ghostscript | 538.7                                    | 49.3          | 8.4      |  |

| Chen    | Web         | 163.6                                    | 764.1         | 82.4     |  |

|         | Wish        | 193.6                                    | 23.0          | 10.6     |  |

|         |             | By Cycle Count (in millions)             |               |          |  |

|         | Ghostscript | 1275.9                                   | 242.2         | 16.0     |  |

| Chen    | Web         | 568.5                                    | 3793.4        | 87.0     |  |

|         | Wish        | 492.5                                    | 138.5         | 21.9     |  |

**Table 1: Percent Time Spent in Kernel Code.** The SPEC benchmarks spend significantly less time in the kernel than a large number of commercial and multimedia workloads, represented here by the IBS, Maynard, and Chen suites. The SPEC and IBS measurements are from [7], the Maynard workloads are from [12], and the Chen measurements are from the data that accompany [4].

nel. Amdahl's law tells us that if we want modern applications such as these to run quickly, the operating system must run quickly as well. Since traditional performance models essentially ignore the operating system and modern OS-dependent applications, a need has arisen for new tools and methodologies that direct their attention at the performance of the OS kernel and the applications that depend on it. The goal of this thesis is to fulfill that need.

In order to develop new tools and methodologies for OS measurement, we must first recognize the unique role played by the OS in a modern system, and consider how existing performance analysis techniques fail to take this role into account. These understandings will provide the foundation for a new set of tools and methodologies that accurately characterize the true nature of OS and OS-dependent application performance.

The modern operating system is, above all else, a provider of abstraction: it takes the raw resources of the low-level hardware and abstracts them into a well-behaved interface for use by the system's resource consumers: user applications and the users themselves. This is a very different role than is played by any other part of the computer system, and, as a result, the designer of an OS kernel faces a unique set of performance challenges that are not conducive to traditional performance analysis techniques. One such challenge arises from the inherent performance penalty imposed by abstraction: the OS designer needs to build abstractions that properly virtualize resources yet at the same time preserve as much of the hardware's raw performance for the end user. A more significant challenge comes in analyzing the abstractions selected for and built into an operating system, for operating system performance cannot be studied in isolation. Because the OS is primarily an abstraction provider, its performance depends directly upon the capabilities of the lowlevel hardware interface that it is abstracting, as well as on the way that the abstractions it creates are used by applications (since not all applications exercise the same OS abstractions). Thus any methodology for analyzing OS performance must take into account both the OS's dependence on features of the underlying hardware architecture as well as on the patterns of application load that indicate which abstractions are important.

Traditional methods for performance analysis are poorly suited to this task. They break down into three basic categories: macrobenchmarking, kernel profiling, and microbenchmarking. Macrobenchmarking, or timing runs of real applications, can be useful for

measuring end-to-end performance on a specific workload, but does not produce enough detail in its results to unravel the complex interactions between the application load and the OS performance, or between the OS and the hardware. Kernel profiling, in which the amount of time spent in each kernel function is measured, gives a highly detailed picture of the kernel's execution, but does not provide the time-sequence information necessary to correlate an application's varying use of kernel abstractions with potential kernel performance bottlenecks. Additionally, standard kernel profiling<sup>1</sup> cannot accurately associate I/O and sleep time with user-process requests, and thus does not provide an accurate mechanism for associating user-visible latency with time spent in kernel routines. Finally, we are left with microbenchmarking, in which the performance of very small pieces of the OS kernel's abstraction layer are measured individually. By itself, microbenchmarking only measures the efficiency of individual kernel abstractions; it ignores how the abstractions are used by user applications, and thus, like the other two techniques, does not indicate how to evaluate and optimize the performance of kernel abstractions under realistic application load.

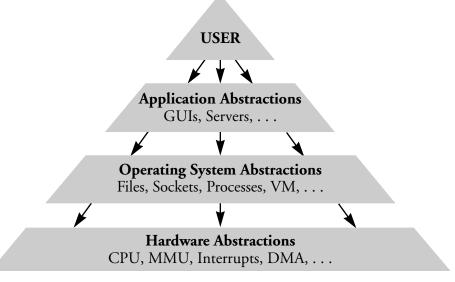

With an understanding of both the demands of OS performance measurement and the flaws in existing measurement techniques, we can now return to the problem of developing tools and methodologies appropriate for analyzing OS performance in its true context, intertwined with hardware performance and OS-dependent application load. The approach that we propose for accomplishing this goal is grounded heavily in the notion of an *abstraction hierarchy*. We can view a complete computer system as a continuum of abstractions stretching from the silicon of the hardware up through the operating system and ending at the application's user interface. The abstractions within this continuum form a natural hierarchy that complements traditional modular design methodology: the hardware provides abstractions of computation and I/O upon which the OS is built; the OS in turn provides virtualized abstractions of physical resources upon which applications are built; finally, applications provide high-level abstractions that organize the OS's abstractions and with which users interact. Figure 1 presents this idea graphically.

1. Some of the problems with traditional kernel profiling are remedied in *pkprof*, a kernel profiler that associates all acquired performance data with user-process requests [16]. However, *pkprof* is currently available only on stock 4.4BSD-Lite running on the MIPS-based DECstation platform, and thus does not provide a general solution to the kernel-profiling problem.

**Figure 1: Computer System Abstraction Hierarchy.** The gray trapezoids represent layers of abstraction; the arrows represent performance dependencies between layers. The user interacts with the application's abstractions, which in turn depend on the operating system's abstractions, which then depend on the hardware's abstractions. This same abstraction hierarchy transforms easily into a performance hierarchy.

The structure of a system's abstraction hierarchy is inherently intertwined with the system's performance, for the performance of any given abstraction depends on the performance of the abstractions upon which it is layered. Thus it is easy to transform the abstraction hierarchy into a *performance hierarchy*, in which the nodes have the same structure as those in the abstraction hierarchy, but the connections between nodes represent the performance dependencies between various abstractions: at each abstraction boundary, the connections to higher level abstractions represent the performance demands of the part of the hierarchy above the boundary, while the connections to lower level abstractions represent the performance resources of the portion of the hierarchy below the boundary.

The performance hierarchy provides an ideal framework for understanding operating system performance, for it captures in one construct the details of the performance interactions between the hardware, operating system, and application. As the application runs, it exercises paths that weave their way from the apex of the hierarchy (where the application's highest-level abstractions or operations are found) through the OS's abstractions and down to the base of the hierarchy (which consists of the fundamental hardware abstractions). By looking at how these paths intersect the hierarchy at the level of the OS-exported abstractions, the operating system designer can determine which abstractions are

critical for the application's performance, and can focus optimization effort appropriately; the application designer can use the same information to optimize his or her application's use of potentially-slow operating system abstractions.<sup>2</sup> Analogously, by looking at how the paths cluster at the bottom of the performance hierarchy, the hardware designer can see where to tune the hardware to maximize the operating system's (and therefore the application's) performance; the operating system designer can use the same data to determine where optimizations to the kernel are warranted.

Thus the first task in understanding the performance of a specific operating system is to construct the performance hierarchy that includes the hardware on which it will run and the primary applications that it will support. The primary technique that we have used to do this is *performance decomposition*, in which the performance of each abstraction in a given level of the performance hierarchy is decomposed into the performance of abstractions in the next-lower level of the hierarchy. This is usually accomplished in one of two ways. Where the performance of an abstraction can be derived analytically from the performance of those below it, the decomposition can be taken directly from the analytic model. In the more common case where analytic models are not available, the dependencies must be reconstructed by varying the performance of the lower-level abstractions (usually by manipulating the hardware platform) while observing the response in the performance of the higher-level abstraction. Chapters 2 and 3 introduce tools and methodologies that help perform such performance decompositions in the operating system and application domains, respectively; they also present case studies that demonstrate the use of the techniques and some interesting sample results.

The technique of developing a performance hierarchy by performance decomposition is a solution to only part of the problem of operating systems measurement, however. While useful to the system designer in that it provides enough information to show where optimizations need be applied, the performance hierarchy approach produces too much detail to be of much use to the less-sophisticated consumer. These consumers include anyone else who cares about operating system performance, from application designers to system administrators; one might think that the kinds of performance results desired by such

<sup>2.</sup> In the context of an extensible operating system, such data would provide important clues as to where specialized extensions and interfaces should be installed.

consumers are mutually incompatible with the details that the performance hierarchy produces for the system engineers. If we consider the types of information that would be useful for such consumers, however, a pattern quickly emerges: all the measurements of interest can be taken at the major abstraction boundaries in the performance hierarchy. For example, an application designer might want to know the performance characteristics of the major abstractions exported by a particular operating system/hardware pairing; these are obtained by taking a horizontal cross-section of the performance hierarchy at the lower (OS) side of the boundary between operating system and application. Similarly, a hardware designer interested in optimizing for the operating system would most likely be interested in a cross-section of the hierarchy at the upper side of the OS-hardware boundary. Finally, a system administrator interested in picking the best OS/hardware pairing to support a given application (such as a web server) might find two cross-sections useful: one at the upper side of the OS-application boundary to characterize the application's demands on the operating system (independent of the OS/hardware platform) and one at the lower side of the same boundary (to characterize the operating system's ability to satisfy the application's demands).

Thus, to complete our methodology of OS performance analysis, we must find a way to distill the detail of the performance hierarchy into a characterization of performance interactions at a given abstraction boundary; ideally, this characterization should take the form of a vector of performance demands by the part of the system above the boundary, a vector of performance resources offered by the part of the system below the boundary, and a way to combine these vectors to get a single, simple metric representing how well the demands are satisfied by the available resources. Although a complete solution to this problem at all abstraction boundaries is well beyond the scope of this thesis, in Chapter 4 we consider the specific case of the application-OS boundary, and derive a methodological approach that transforms the performance hierarchies for an application and an OS into a single metric that predicts user-visible system performance.

Thus throughout this thesis we present methodologies and tools explicitly designed for building and analyzing the performance hierarchies that define modern system performance. We begin in Chapter 2 with techniques to characterize and link together the foundation layers of the hierarchy: the hardware and the operating system. Next, in Chapter 3,

we extend the hierarchy to include the performance abstractions of OS-dependent user applications by presenting techniques for decomposing user-visible application performance into dependencies upon the operating system. Finally, in Chapter 4 we take the performance hierarchy obtained by the techniques in the earlier chapters and discuss a methodology that is capable of reducing the intricate detail of the performance hierarchy into a set of simple characterization vectors that can be transformed into a single application-specific metric for gauging or predicting operating system and application performance. The result of the analysis in these three chapters is thus a methodology that restores relevancy and rigor to operating system measurement: it discards *ad hoc*, artificial measurement in favor of a well-defined blueprint for analyzing operating system performance in the context of real hardware and real application load, and, as a result, produces metrics that can be used in a meaningful way for system performance evaluation and comparison.

## Chapter 2

# Decomposing the Performance of the Operating System Kernel

The first step in understanding operating system performance is to understand how the performance of the operating system's major abstractions depends on the performance of the underlying hardware platform. Gaining this understanding is a prerequisite for constructing the lower half of the system performance hierarchy, which encompasses both the hardware and operating system layers. The methodology that we have chosen to accomplish this task is based heavily on the notion of performance decomposition, and relies on microbenchmarking for its tools. Although we have seen how microbenchmarks used in a vacuum do not provide the information needed to understand the interactions and performance characteristics of a given system, when combined with the performance decomposition technique they provide the means that we need to achieve the desired characterization of the lower half of the system performance hierarchy.

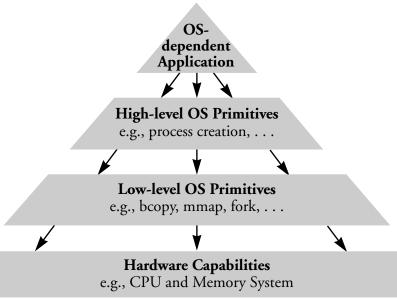

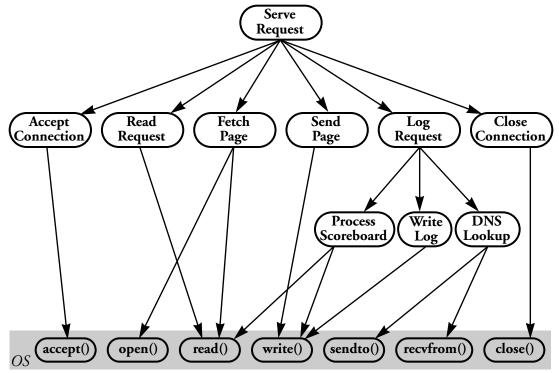

The microbenchmarks that we use (*hbench-OS*, described in Section 2.2) divide roughly into two areas: one set quantifies hardware capabilities and performance (e.g., memory bandwidth), while the other measures the primitive functionality that is exported from the kernel to applications (such as the system calls, process creation, and file/network access). The results produced by these two sets correspond naturally to the bottom layers of the system performance hierarchy; Figure 2 depicts the structure of this piece of

**Figure 2: Decomposition of OS Performance via** *hbench-OS* **Primitives.** The performance of OS-dependent applications can be decomposed into high-level OS-provided services and primitives, which can in turn be decomposed into low-level kernel primitives (that may themselves be used by applications). These low-level kernel primitives can, in turn, be decomposed again into hardware capabilities. In many cases, *hbench-OS*'s suite of tests allows us to measure and relate the lower three levels of this hierarchy.

the hierarchy as a pyramid of relationships between layers representing components of OS performance.

The performance decomposition methodology enters when we need to reconstruct the interdependencies in the OS/hardware portion of the performance hierarchy, a task for which the microbenchmarks themselves do not provide any guidance. As described in Chapter 1, this task can be approached from two directions, analytically or experimentally. We will use both techniques, but will direct our focus on the experimental model, for it is rare that the performance of such a complex system as the combination of OS and hardware can be predicted analytically. The key idea in performing a performance decomposition experimentally is to use controlled variation of the performance of a low-level primitive or abstraction in order to gauge its impact on, and thus its connections to, higher-level primitives or abstractions. Thus our decomposition methodology consists of two steps: first, using our *hbench-OS* benchmarks to measure performance at each of the lower levels of the hierarchy while varying features of the hardware in a controlled manner (i.e., changing only one component of the test system at a time); and second, using the changes in hardware as well as software analysis (via hardware counters, software profiling, or code analysis) to relate the performance of primitives in a given layer to the perfor-

mance of primitives in layers above and below it. Once the interaction between each pair of adjacent layers is understood, the hierarchy of performance dependencies can be reconstructed.

In many cases, our *hbench-OS* benchmark tests provide enough detail about the internal structure of individual layers of the hierarchy so that it is possible to analytically reconstruct the performance dependency paths that connect application-visible OS abstractions and primitives to hardware performance; this is especially true when the primitives being evaluated are related to bulk data transfer, as will be seen in the case study below. In other cases, however, the tests by themselves may only be capable of measuring the performance of the top-layer abstraction, and thus we are forced to rely on the experimental technique, bypassing the middle layers of the hierarchy to directly determine the hardware dependencies of the upper-layer primitives; as an example, we found it necessary to resort to this technique to relate the lowest-level primitives measured by *hbench-OS* (such as raw memory bandwidths) to features of the hardware architecture.

With this methodology for building the lower levels of the system performance hierarchy in hand, we are now ready apply it to a real system. Before doing so, however, we first present some other approaches to OS performance evaluation, and discuss how our decompositional methodology differs from these traditional techniques. Next, in Section 2.2, we describe in greater detail the *hbench-OS* tools that we have developed for measuring the performance of OS primitives. These tools are based on the *lmbench* benchmark suite [14], but have been significantly enhanced and modified; we describe these modifications as well. Finally, in Section 2.3, we apply our tools and methodology to the task of understanding and decomposing the performance of the NetBSD operating system [15] on the Intel x86 platform. In this last section, we also demonstrate the types of detailed conclusions that the performance-hierarchy approach allows us to draw about the interactions between OS and hardware performance, and how these conclusions provide guidance for future hardware and software tuning; we defer discussion concerning the OS's impact on application performance to Chapters 3 and 4.

#### 2.1 Related Work: Benchmarking Operating Systems

The operating systems research community has not ignored OS performance; on the con-

trary, there is a large body of work aimed at understanding OS performance and its hardware dependencies. The typical approach that has been taken is the microbenchmarking approach: various OS primitives are measured across a wide range of hardware platforms, and any trends in the data are used to draw conclusions relating OS performance to hardware performance. Probably the most frequently cited example of this type of work is Ousterhout's 1990 paper "Why Aren't Operating Systems Getting Faster As Fast As Hardware?" [17] in which Ousterhout uses a set of tests (originally designed to measure the performance of the Sprite operating system) to analyze the performance of OS primitives across a range of then-common processor and system architectures, primarily to determine the performance impact of the move from CISC to RISC architecture. Ousterhout's benchmarks isolate a number of kernel primitives and, when run across multiple platforms, provide some indication of the dependence of OS performance on machine architecture. However, they do not include enough detailed tests to characterize the capabilities of the underlying hardware and to use that characterization to understand the performance of higher-level kernel primitives; thus they are not useful for the performance decomposition approach.

Anderson et al. pursued a similar approach in order to examine the interplay of hard-ware architecture and the operating system in a multiprocessing microkernel design [1]: they used a set of *ad hoc* microbenchmarks to perform a cross-platform comparison of OS primitives targeted to microkernel bottlenecks (IPC and communications latency, thread overhead, etc.). Again, the benchmarks they used were not complete enough to provide the detail necessary for constructing a full system performance hierarchy.

In 1995, McVoy improved the state-of-the-art in OS microbenchmarking with the introduction of his *lmbench* package: a suite based on a broad array of portable OS microbenchmarks capable of measuring both hardware capabilities (e.g., memory bandwidth and latency) and OS primitives (e.g., process creation and cached file reread) [14]. Although *lmbench*'s detailed tests offered the breadth and detail needed to decompose operating system primitives into their hardware-dependent components, McVoy used them primarily to draw conclusions about the relative merit of various operating system and hardware architectures. Additionally, the *lmbench* tests suffer from several statistical and methodological flaws that make them difficult to use as the basis of a performance

decomposition methodology; we discuss these flaws and our attempts to fix them in Section 2.2.

Although the microbenchmarking approach used by these researchers is similar to the one that we have chosen, there are two important differences. First, and most important, in this chapter we are not trying to make general claims about operating system performance. This type of conclusion can only be made when the OS is considered in the context of realistic application load, which we do later in Chapters 3 and 4; here, we are instead trying to reconstruct the dependencies of OS abstractions on hardware, without making any claims about the relative or absolute importance of any given abstraction. The other difference is in the methodology that we use to determine the performance dependencies: instead of trying to draw conclusions from comparisons across widely divergent hardware platforms, as do McVoy, Ousterhout, and Anderson, we rely on the principle of controlled experimentation, making the smallest possible changes to the hardware platform that produce noticeable performance differences. This technique is essential in order to control as many extraneous variables as possible; otherwise, it is impossible to isolate the effect of specific hardware features on OS performance, and the details of the connections between OS performance and hardware are lost.

#### 2.2 Microbenchmark Tools: Revising lmbench into hbench-OS

Since microbenchmarks play such a key role in the decomposition-based methodology that we have developed, our first task in implementing the methodology was to construct a set of rigorous microbenchmark programs capable of producing accurate, reproducible results. We initially chose McVoy's *Imbench* [14], described above in Section 2.1, for the breadth of its tests and the detail they claimed to provide. However, as we began to use *Imbench* to study NetBSD's performance for the case study in Section 2.3, we found that it had several shortcomings as a tool for the detailed scientific study of OS-hardware interaction, which is what we needed to construct the lower levels of the system performance hierarchy. Most notably, it did not provide the statistical rigor and self-consistency needed for detailed architectural studies. To resolve these shortcomings, we decided to revise *Imbench* into a suite of tests that would be useful for both cross-platform comparison and detailed system analysis—we wanted to fulfill the *Imbench* promise of providing a set of

| Test                         | Description                                                                                                                               |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memory read/write bandwidths | Determines the bandwidth to memory by timing repeated summing of a large array.                                                           |  |  |

| bcopy() bandwidth            | Determines the memory bandwidth achieved by the bcopy() memory copy routine.                                                              |  |  |

| File reread bandwidth        | Measures the bandwidth attainable in reading cached files from the system buffer cache.                                                   |  |  |

| TCP bandwidth                | Measures the bandwidth attainable through an already-established TCP connection through the loopback interface.                           |  |  |

| Cached mmap-read bandwidth   | Measures the bandwidth attainable when reading from a cached file mapped into the process's address space                                 |  |  |

| Process creation             | Measures the latencies of three different methods of process creation: via a simple fork(), fork()+exec(), and system().                  |  |  |

| Signal handler installation  | Measures the latency of installing a new signal handler from a user process.                                                              |  |  |

| TCP connection latency       | Measures the latency of setting up a TCP connection across the loopback interface.                                                        |  |  |

| Null system call latency     | Measures the latency of writing one byte to /dev/null, to approximate the cost of entering the kernel through the system call dispatcher. |  |  |

**Table 2: Summary of a subset of the original** *Imbench* **benchmarks** [9]. Both the *Imbench* and *Imbench* suites include many other benchmark tests; those listed above are the most useful, and are the ones used in this thesis.

tools capable of illuminating the inner workings of an operating system in order to bring to light how that operating system's performance depends on the hardware upon which it runs. Since *lmbench* provides a sufficiently complete set of tests to cover a broad range of operating system functionality, our modification efforts were directed at making the existing tests more rigorous, self-consistent, reproducible, and conducive to statistical analysis.

The specific problems that we encountered with *lmbench* ranged from minor (we found the output format of the benchmarks difficult to analyze) to substantial (with a reasonable compiler, the test designed to read and touch data from the file system buffer cache never actually accessed the data). Our biggest concerns, however, were with the benchmarks' measurement and analysis techniques: we were not confident that the methodology used in a number of tests was rigorous enough to produce accurate, reproducible results. In the following sections we document the difficulties that we encountered and the methods that we used to solve them. The original *lmbench* tests that are used in this thesis are summarized in Table 2; we refer the reader to McVoy's original *lmbench* paper [9] for a more detailed description of the benchmark tests discussed.

For the remainder of this section, we will use *lmbench* to refer to the original *lmbench-1.1* test suite, and *hbench-OS* to refer to the modified test suite. Also, we will refer to the on-chip cache as the L1 (first level) cache and the secondary cache as the L2 (second level) cache.<sup>3</sup> Note that the Pentium Pro integrates the L2 cache into the same package as the CPU, while earlier CPUs use an external L2 cache.

#### 2.2.1 Timing Methodology

Lmbench performs all of its timing using the gettimeofday () system call to sample the system time before and after the operation that is being measured. On systems that do not have (or use) hardware microsecond timers, the resolution of gettimeofday () is only that of the system clock—as coarse as 10 ms in some cases. One particularly severe real-life example that demonstrates the problems imposed by a coarse-grained timer can be seen in the DEC Alpha 21164 running Digital UNIX 3.2F; the resolution of gettimeofday () on such systems is 1 ms. This is far too coarse to accurately time individual low-latency events or to measure high bandwidths, as some of the *Imbench* tests attempt to do. For example, the *Imbench* TCP connection latency benchmark times individual connection requests through the loopback interface (a software-simulated network interface that reroutes outgoing data back into the system's input queues, bypassing the real network interface and physical medium entirely). As these take much less than 1 ms, *Imbench* reports a 0 microsecond connection latency on the Alpha. Similarly, the memory bandwidth benchmark times a single buffer read; if the test is run with buffers small enough to fit in the L1 or L2 cache, *Imbench* on the Alpha reports infinite bandwidth.

We made two modifications to avoid the timer resolution constraint imposed by gettimeofday(). First, we modified each benchmark to run its tests in an internal loop, timing the entire loop and reporting the average time (total time divided by number of iterations). While many of the *lmbench* latency tests already used such internal loops, the loops were run an arbitrary, predetermined number of times, causing scalability problems on different-speed systems. To fix this, we modified the internal loops to run for a

<sup>3.</sup> A *cache* is a piece of small, high-speed memory that is used to reduce the access time to frequently used data normally stored in slow main memory (DRAM). As data is retrieved from DRAM, it is cached in the CPU's caches under the assumption that it will be reused in the near future; subsequent accesses to the data incur only the cache's low latency, not the DRAM's high latency. A system usually has two or more levels of caches; the L1 cache (closest to the CPU) is the smallest and fastest, and those at higher levels are slower but larger.

minimum of one second, calculating the number of iterations dynamically. The dynamic calculation of the iteration count ensures that the running time of the benchmark will exceed any reasonable timer resolution by a factor of 10 or more, regardless of the system or CPU being used. In addition, the inclusion of internal iteration with the bandwidth tests makes possible precise measurement of the memory and copy bandwidths to the L1 and L2 caches.

For benchmarks where the measurement is destructive and can only be taken once (for example measuring the virtual memory and TLB overhead in reading a memory mapped region), the loop-and-average method is not effective. For these tests, we had to appeal to a hardware-specific solution to gain the timing accuracy needed: we introduced hooks to allow hardware cycle counters (which tick at the CPU's internal clock speed) to replace gettimeofday() for timing. Currently *hbench-OS* only supports the Pentium and Pentium Pro counters, but adding support for other architectures (such as the Alpha or SuperSPARC) is not difficult. Note, however, that if an architecture supports no hardware counters/timers, it is not possible to measure such destructive events accurately.

Adding the hardware-timer hooks also significantly enhances the flexibility of the *hbench-OS* package, as the high-resolution timers give *hbench-OS* the capability of measuring events with low latencies without the need to run the event in a loop, thus allowing collection of cold-cache performance numbers. When using the gettimeofday() timing method, only warm-cache results can be measured, as the loops that are required for accuracy also allow the benchmark to run entirely from the cache.

Our last modification to the timing routines was to include code to measure and remove the overhead introduced by the timing mechanism (either the gettimeof-day() system call or the instructions to read the hardware counters). Removal of this timer overhead is essential, especially when using the hardware timers to measure single low-latency events. When combined with the use of the hardware counters, this allows for precise timing measurements: on a 120 MHz Pentium, for example, our timings are accurate to within one clock cycle, or 8.3 ns.

#### 2.2.2 Statistical Methodology

With the timing irregularities solved through iteration and the use of hardware counters, we discovered another shortcoming in *Imbench*'s methodology: it was inconsistent in its statistical treatment of the data. Several of the benchmarks reported the result of one measurement, others reported the average of multiple repeated measurements, and yet others reported the minimum of multiple repeated measurements. We wanted to run each test a number of times to obtain more statistically sound results, but with the goal of applying a consistent policy to the data analysis. To achieve this goal, the benchmarks were each restructured to make a single timing measurement. The tests are run multiple times by a driver script (each run in a new process), and the result from each run is appended to a file. Since our reformulation of the tests preserves the value from each run of the benchmark, we have divorced the data analysis policy from the benchmark itself.

The most-used statistical policy in *lmbench* is to take the minimum of a few repetitions of the measurement; this is intended to pick out the best possible result by ignoring results contaminated by system overhead. However, in doing so it can pick out results that are flukes—especially when the measurement involves subtracting an overhead value, as in the context-switch latency benchmark. If the actual overhead on a specific run is lower than the pre-calculated overhead, an abnormally good result will be obtained when the pre-calculated overhead is removed from the result. To avoid these problems, in most cases we take an n%-trimmed mean of the results: we sort the results from a benchmark, discard the best and worst n% of the values, and average the remaining (100-2n)%. n is typically 10%. With this policy, we discard both the worst values resulting from extraneous system overhead as well as the overly-optimistic results.

For certain benchmark tests, however, a simple trimmed mean is not sufficient to capture all of the important features of the results. This is particularly noticeable when the results of a test do not approximate a normal distribution, but are (for example) bimodal. Such cases are easily detected by their large standard deviations, and since all data is preserved, it is easy to view the actual distribution of the data to determine the best interpretation. We encountered this problem in measuring L2 cache bandwidth, as cache conflicts within our test buffer produced a bimodal distribution where the true bandwidth was represented by a large, narrow peak and the false (conflict) bandwidth was represented by a

lower peak with larger spread. In this case, we merely increased the percentage that was trimmed from the data in order to isolate only the true bandwidth peak.

Finally, we have modified the benchmarks (where possible) to perform one iteration of the test before beginning the real measurement. Since we run most of the tests in loops anyway, we expect warm-cache results. Running the test once before commencing measurement ensures that the caches are primed and that any needed data (e.g., files in the buffer cache) are available.

Note that in gathering the results in this chapter, we ran each benchmark (each of which runs a large number of internal iterations) fifty times on all machines but the 386-33 and 486-33 (due to limited access to the hardware, only five iterations were performed on these machines), and we report the 10% trimmed average across these iterations. Standard deviations are represented by error bars in the graphs; in all cases standard deviations were less than 1% (and are frequently not visible in the graphs) except in the file reread benchmark, which produced standard deviations of less than 5%.

#### 2.2.3 Increased Parameterization

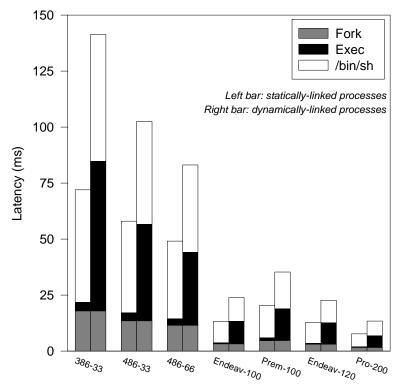

In order to make the *lmbench* tests more amenable to our investigations, we made several modifications to increase the flexibility of the benchmarks by making them more parameterizable. For example, we modified the pipe, TCP, and file-reread bandwidth tests to accept a transfer size as an argument in order to investigate the effect of write-back caches on small-buffer transfers. We also modified the memory read/write/copy bandwidth tests to allow for measurement of the L1 and L2 cache bandwidths. Finally, we modified the process creation benchmark to allow for measurement of both dynamic and statically-linked processes.

#### 2.2.4 Context Switch Latency

Measuring context switch latency is particularly challenging, as the latency of a context switch is not very well-defined. In the strictest sense, context switch latency is the time that it takes for the OS to suspend and save the hardware state of a running process (e.g., registers, stack pointer, page table pointers), select a new process to run, load the new process's saved hardware state, and then begin executing it. *Lmbench* uses a looser definition of context switch latency: in addition to the above components of context switch time, it

includes the latency that results from faulting the working set of the new process into the CPU's cache. This cache-filling overhead is not strictly a part of context-switch time, for it only occurs when the two processes collide in the cache; thus, it is a function of the sizes of the processes' working sets and the OS's page-mapping policy, and not of the hardware or of the OS's context-switch code. What *Imbench* measures is closer to what a user might see for context-switch time with several large, data-intensive processes than to the raw context-switch speed of the OS.

Although measuring cache conflict overhead is useful (especially for estimating context-switch time for large processes), *Imbench*'s context switch benchmark demonstrates that there are problems with this approach that make it infeasible for a portable context switch benchmark. The most significant problem occurs when the operating system does not support intelligent page coloring, i.e., it chooses physical addresses for virtual pages randomly.<sup>4</sup> To understand why this is a problem for *Imbench*, we need to investigate how *Imbench* collects its context switch latency data.

The *Imbench* context switch latency benchmark measures the time to pass a token around a ring of processes via pipes; to duplicate the effect of a large working set, each process sums a large, private data array before forwarding the token, thereby forcing the pages of the array into the cache. When the total time for this operation is divided by the number of processes in the ring, *Imbench* is left with a number that includes the raw context-switch time, the time to fault the array into the cache, the time to sum an already-cached array, and the time to pass a token through a pipe. The latter two factors are measurement overhead and must be removed. To do so, *Imbench* passes a token through a ring of 20 pipes within one process, summing the same data array each time the token changes pipes, then divides by the number of times the token went through a pipe. The problem with this approach is that the test assumes that summing the buffer produces no unnecessary cache conflicts, for the summing overhead should not include any cache-fill time. However, if the virtually-contiguous pages of the buffer are randomly assigned to physical addresses, as they are in many systems, including NetBSD, then there is a good probability that pages of the buffer will conflict in the cache, even when the size of the buffer is

<sup>4.</sup> It is also this random page-mapping policy that introduces the somewhat large (5%) standard deviations that we see in the file reread benchmark.

smaller than the size of the caches [3]. Thus the overhead will contain some cache-fill time, and as a result might be too high; if the actual context switch test obtains good page mappings, the overhead may even be so high that when *lmbench* subtracts it from the total time to get just the context-switch latency, the resulting (reported) context switch latency is negative or zero. A similar problem exists if the overhead-measurement test obtains good page mappings while the real context switch latency test obtains conflicting mappings; here the overhead will be too small, and the reported context switch latency will be too large.

Because with *lmbench* there is no guarantee of reproducible context-switch latency results in the absence of OS support for intelligent page coloring, we decided, in hbench-OS, to restrict the test to measure only the true context switch time, without including the cost to satisfy extra cache conflicts or to fault in the processes' data regions, as these can be approximated from the cache and memory read bandwidths. To this end, we introduced a new context switch latency benchmark to supplement the existing *lmbench* test. We did not replace the *lmbench* test completely, as it can be useful in estimating user-visible context-switch latencies for applications with a known memory footprint, and for determining cache associativity. In our new test, context switch latency is a function of the speed of the OS in selecting a new process and changing the hardware state to run it. To accomplish this, we carve each process's data array out of a large region shared between all the processes in the ring. To compute the overhead for *nproc* processes, we measure the time to pass a token through *nproc* pipes in one process, summing the appropriate piece of the shared region as the token passes through each pipe. Thus we duplicate exactly what the real context switch test does: we use the same memory buffers with the same cache mappings, and touch them in the same order. When we subtract this overhead from the context switch measurement, we are left with the true context switch time plus any hardwareimposed overhead (such as refilling non-tagged TLBs and any cached data that got flushed as a result of the context switch but not as a result of faulting in the process). With these modifications, we can obtain results with a standard deviation of about 3% over 10 runs, even with large processes, and without having to flush the caches. In contrast, on the same machine, *Imbench* reports results with standard deviations greater than 10%.

#### 2.2.5 Memory Bandwidths

In the interest of consistency, we made some modifications to the benchmarks that touch, read, or write memory buffers. The *Imbench* bandwidth tests use inconsistent methods of accessing memory, making it difficult to directly compare the results of, say memory read bandwidth with memory write bandwidth, or file reread bandwidth with memory copy bandwidth. The tests that read memory primarily use array-offset addressing to iterate through the buffer, while the write and copy-based benchmarks dereference and increment pointers. On pipelined or superscalar architectures, using array-offset addressing produces address generation interlocks (due to the implicit add), while using pointers can cause false data dependency interlocks. The difference between the two approaches is evident upon examination of the compiler's output for the two benchmarks: gcc (on the x86) implements the array-offset addressing in the C statements (ebx [0] = 1; ebx [1] = 1;) as:

```

movl $1, (%ebx)

movl $1, 4(%ebx),

while a similar example using pointers (*ebx++ = 1; *ebx++ = 1;) is imple-

```

```

movl $1, (%ebx)

addl $4, %ebx

movl $1, (%ebx)

addl $4, %ebx.

```

mented as:

Depending on how the processor's pipeline handles interlocks, the two methods can produce different timings. For example, on the Alpha processor, memory read bandwidth via array indexing is 26% faster than via pointer indirection; the Pentium Pro is 67% faster when reading with array indexing, and an unpipelined i386 is about 10% faster when writing with array indexing. To avoid errors in interpretation caused by these discrepancies, we converted all data references to use array-offset addressing. In addition, we modified the memory copy bandwidth to use the same size data types as the memory read and write benchmark (which use the machine's native word size); originally, on 32-bit machines, the copy benchmark used 64-bit types whereas the memory read/write bandwidth tests used 32-bit types.

#### 2.2.6 New Output Format

*Lmbench* placed all of its output into one large file whose name identified the machine being benchmarked. In this format, the raw data was not very easy to extract for graphing or statistical analysis. Thus we decided to revamp the output format to make it easier to generate and process the raw data automatically.

In our new scheme, the user can specify in a configuration file exactly which tests are to be run; the driver script is automatically generated from this script. Each machine tested is assigned its own directory. Although the benchmark results are still stored initially in one large file, a script is provided to separate the large file such that the results from each parameterization of each benchmark are placed in a separate file whose name includes the name of the test and the parameters. Each file contains *n* numbers where *n* is the number of runs that were made of the benchmark. For example, if 10 runs were made of the context switch latency benchmark with 32 processes of size 16 KB, there would be 10 numbers in the file lat\_ctx\_16k\_32. Several other files are used to hold the version/RCS and system configuration information. Each of the benchmark result files is processed by a script that sorts the values, strips the low and high tails, and calculates the average and standard deviation as described in Section 2.2.2; these processed results are placed back into individual files, which are then combined into a summary file. Another script produces an *lmbench*-style summary report from this. Thus the summary output is still available to the end user, but the raw data is preserved and made available to the researcher who wishes to use it; the use of the file-system namespace as a database of results allows easy selection of datasets for graphing or analysis of the raw data.

## 2.3 Case Study: Constructing a Performance Decomposition for NetBSD on the Intel x86 Platform

With both the decomposition methodology discussed at the beginning of this chapter and the *hbench-OS* tools described above in hand, we now turn to a case study in order to illustrate both the interaction between the tools and the methodology as well as the type of results that emerge in the process of constructing the lower levels of the system performance hierarchy. For our subject operating system, we chose NetBSD 1.1 [15], a derivative of the CSRG 4.4BSD-Lite release [5], which shares a common ancestry with many of today's commercial UNIX implementations. We selected NetBSD for its openness and its

| Name-MHz   | Caches Features        | Memory/<br>Bus-MHz | Processor        |

|------------|------------------------|--------------------|------------------|

| 386-33     | no L1                  | 70 ns              | i386DX           |

|            | 64K async. L2          | 33 MHz             |                  |

| 486-33     | 8K combined L1         | 60 ns              | i486DX           |

|            | 256K async. L2         | 33 MHz             |                  |

| 486-66     |                        | 60 ns              | i486DX2          |

|            |                        | 33 MHz             |                  |

| Endeav-90  | 16K split L1           | 60 ns EDO          | Pentium          |

|            | 512K pipeline-burst L2 | 60 MHz             | (i430FX chipset) |

| Endeav-100 |                        | 60 ns EDO          | Pentium          |

|            |                        | 66 MHz             | (i430FX chipset) |

| Endeav-120 |                        | 60 ns EDO          | Pentium          |

|            |                        | 60 MHz             | (i430FX chipset) |

| Prem-100   | 16K split L1           | 70 ns              | Pentium          |

|            | 512K async. L2         | 66 MHz             | (i430NX chipset) |

| Pro-200    | 16K L1, 256K L2, both  | 60 ns EDO          | Pentium Pro      |

|            | writeback and on-chip  | 66 MHz             | (i440FX chipset) |

**Table 3: Features of Test Machines.** Note that the 100 Mhz Pentiums run the memory bus at 66 MHz as opposed to the 60 MHz of the other Pentium processors. Unless otherwise noted, all L1 caches are write-through.

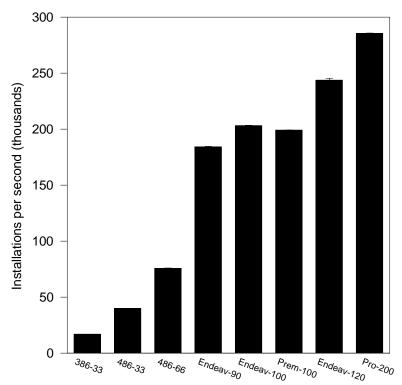

multiplatform support: having the source code meant that we could use kernel profiling and source code analysis to verify our techniques, and its multi-platform support provided the possibility of future cross-architecture comparisons. For our hardware test platforms, we selected eight machines from the Intel x86 architectural family: a 386, two 486's, four Pentiums, and one Pentium Pro. The hardware details of these machines are given in Table 3. We selected the Intel x86 architecture as our subject architecture due to its breadth: in its evolution from the i386 through the Pentium Pro, the Intel x86 architecture has progressively included more and more of the advanced features that characterize a modern architecture, including pipelining, superscalar execution, and an out-of-order core with an integrated second-level cache. It thus allows us to build a set of performance hierarchies that include most of the hardware features that are typically found in modern microprocessors. All of our machines ran the same NetBSD-1.1PL1 "GENERIC" kernel; we did not optimize the kernels for their target platforms, for we were particularly interested in the effects of hardware evolution on operating system performance in the absence of processor-specific optimizations.<sup>5</sup>

As described earlier in this chapter, the experimental approach to performance decomposition requires controlled variation of hardware features in order to isolate the dependencies of OS primitives on those features. The set of test platforms that we used were carefully selected to allow for such controlled variation. For example, the use of several different motherboards with the same CPU and several different CPUs with the same motherboard allowed certain comparisons to reveal dependencies on features of the CPU architecture and the memory system. For example, comparing the 100 MHz Endeavor Pentium with the 100 MHz Premiere-II Pentium reveals the effect of pipelining the L2 cache and installing EDO memory; similarly, comparisons between the 90, 100, and 120 MHz Endeavor Pentiums reveal the effects of increasing the CPU clock rate while holding the memory system constant. The specific comparisons that we used and the connections that they allowed us to form in the performance hierarchy are detailed in the following sections.

#### 2.3.1 Bulk Data Transfer

We begin our study with an example of the best-case performance decomposition methodology, where the performance of high-level OS primitives can be tracked analytically all the way down to hardware dependencies and then verified experimentally. The most illuminating example of this is the case of bulk data transfer. We choose bulk data transfer as an illustrative OS primitive since it is an essential component of the performance of bandwidth-sensitive applications such as web servers and multimedia/network video applications. When running a heavily-used web server, bcopy is the most-frequently called kernel function, accumulating more than 55% of the total in-kernel time. Even typical development work involves large amounts of bulk data transfer: our kernel profiling results under NetBSD indicate that the kernel can spend as much as 23% of its time in bcopy while supporting a mix of editing, compiling, debugging, and mail.

Applications that rely on bulk data transfer use one of three methods to access their data: reading from a file in the file system, sending and receiving data on a TCP connection, or mapping a file into their address spaces. Since each of these data-access methods

<sup>5.</sup> This issue is especially important for portable OS's that may not be tuned for a particular architecture (e.g., Linux, Windows NT, UNIX), as well as for OS software that can reasonably be expected to outlive the hardware for which it was originally optimized (e.g., Windows 3.x).

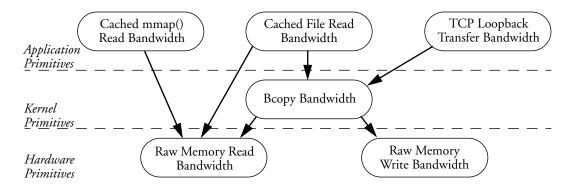

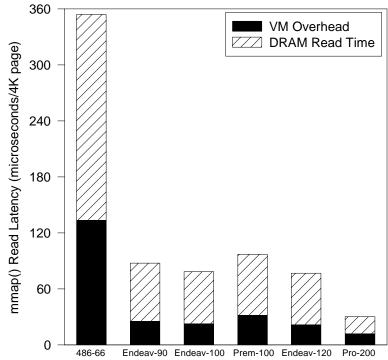

**Figure 3: Decomposition of Application Data-access Primitives.** All of the application-level data primitives for bulk data access depend on the hardware's memory read bandwidth since they all touch data. File reading interposes the extra overhead of a cross-protection-domain bcopy to move the requested data to user-space buffers; TCP transfer interposes three bcopy's as it shuffles the data through the loopback interface and between user and kernel space; mmap adds virtual memory system overhead as it enters new mappings into the process's address space.

involves a significant number of memory accesses, we can base our decomposition on the *hbench-OS* tests that measure the hardware memory read, write, and copy bandwidths. If we ignore the effects of disk and network latency (since we run all of our disk tests within the buffer cache and all of our network tests on the software loopback interface, which bypasses the physical network medium), we arrive at the decomposition shown in Figure 3. There is also a CPU computation component in each of the application-level primitives; it is most significant in the TCP test due to the complexity of protocol encapsulation and checksumming.

#### Hardware Bandwidth Capabilities

The hardware's ability to move data is a function of the main memory speed, the memory bus bandwidth, the size of the L1 and L2 caches, the write policy of the caches (e.g., write-back, write-through, write-allocate), and the processor's ability to efficiently use these resources (i.e., via pipelining or reordering memory operations). It is not possible to directly measure any one of these features; *hbench-OS* measures the interaction of all the components of a particular system. However, by using comparisons between different system configurations, we can measure how each component affects performance.

The *hbench-OS* tests that can be used to quantify the hardware's capability for bulk data transfer, i.e., those that measure the bottom layer of Figure 3, are the raw memory bandwidth tests, which measure effective software read and write bandwidths—the attainable bandwidths when array-addressing operations (needed to index through memory) are

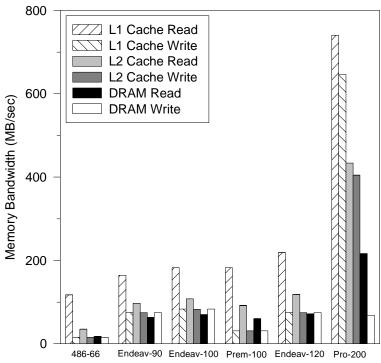

**Figure 4: Raw Memory Bandwidth.** The 64-bit, burst-capable memory bus of the Pentiums produces a factor of four improvement in L2 and DRAM read memory bandwidth from the i486 architecture. The combination of pipeline-burst cache and EDO DRAM gives the *Endeav-100* a significant performance advantage over the *Prem-100*; its higher memory bus clock allows the *Endeav-100* to outperform its 90 and 120 MHz siblings. The Pentium Pro exhibits exceptional cache performance and good memory read bandwidth (due to its out-of order prefetching memory unit), but suffers on memory writes due to an unnecessary cache coherency protocol that prevents back-to-back bus write transactions.

inserted between each memory reference. Although the raw hardware transfer bandwidths are potentially higher, the software bandwidths are more representative of what is attainable by actual code.

Figure 4 plots the peak raw bandwidths for reading from and writing to both caches and main memory of several of the test machines. The almost 4-fold improvement in L2 and main memory read performance between the 486-66 and the *Prem-100* is due to increased bus bandwidth and bus burst capability. The Pentium system has a 64-bit data bus, twice as wide as the 486's 32-bit bus; in addition, the Pentium supports burst transfers from the system's fast page mode DRAM, while the 486 does not. The measured write performance only doubles from the 486-66 to the *Prem-100*, because the older chipset on the Premiere system does not burst writes to DRAM; only the wider path to memory plays a role in the speedup compared to the 486.

The write performance of the *Endeav-100* doubles that of the *Prem-100* because of the Endeavor motherboard's pipeline-burst L2 cache and EDO DRAM. The pipeline-

burst cache can latch three out of every four memory references in one bus cycle each and then burst them off to the DRAM. This explains why the main memory write bandwidth is comparable to the L2 cache's inherent read bandwidth—the pipelined cache is hiding much of the already-low DRAM latency from the CPU. Note that on the *Endeav-120*, which shares the same memory subsystem as the *Endeav-100* and *Endeav-90*, the DRAM and L2 read bandwidths are higher than expected from comparison with the *Endeav-90*, since the processor is clocked at an integral multiple of the memory bus speed. This allows the *Endeav-120* to utilize more of the bus bandwidth (61% vs. 54% for the *Endeav-100*, as determined with the Pentium hardware event counters) since CPU and bus cycles coincide more frequently.

It is interesting to note that in the raw memory bandwidth tests, the dual-issue capability of the Pentium is being very poorly utilized. We instrumented *hbench-OS* with the Pentium's built-in hardware counters, and discovered that when memory is accessed by summing an array using array-offset instructions, less than 0.1% of the memory instructions are parallelized. Similar results are found when the built-in string opcodes are used. Parallelism can be increased to nearly 50% by using pointer arithmetic to step through the array. In this case, each pointer increment is issued along with a memory reference, and is essentially free; however, two memory references are never issued simultaneously. In addition, this extra parallelism is introduced at the cost of an extra stall cycle on each memory access due to address generation interlocks. Thus both methods of memory access provide approximately the same performance, so we predict that memory intensive workloads may profit less than expected from the superscalar architecture of the Pentium.

This conclusion also raises the interesting issue of the usefulness of micro-optimizing compilers for the OS kernel. We experimented with the PCG version of pgcc (an adaptation of the GNU gcc compiler that performs aggressive instruction scheduling for the Pentium pipelines) and discovered that pgcc's optimizations had essentially no effect on the performance of the memory-intensive benchmarks, even when the memory accesses were explicitly coded (as opposed to using the built-in string operations). The problem is that the hardware itself does not allow dual-issue of memory references in the cases we tested, and thus no instruction scheduling policy could improve performance in these cases.

Returning to the data in Figure 4, we see that the most spectacular feature is the performance of the Pentium Pro system. The *Pro-200* exhibits a strange combination of impressive across-the-board memory bandwidth, except for uncharacteristically poor main memory write bandwidth. The *Pro-200*'s nonblocking write-back L1 cache gives it an extreme performance advantage over the Pentiums on small cached reads and writes. The *Pro-200* L2 cache also significantly outperforms that of the Pentiums, as the Pentium Pro runs its on-chip, lockup-free L2 cache at the CPU clock speed, as opposed to the system bus speed. Also, while the Pentiums' non-write-back caches access memory on every write, the Pentium Pro's write-back caches are intelligent enough to combine writes into cache-line-sized increments, resulting in cached write performance that nearly equals cached read performance, as the write-back cache is not forced to read a line before writing to it. The astounding cache performance on the *Pro-200* suggests that write-back caches offer a major performance advantage to those applications that perform bulk data transfer in small, cache-sized chunks, for example, the size of a typical HTML file; our later application measurements in Chapter 4 confirm this hunch.

Along with its high cache performance, the *Pro-200* also sports exceptionally high main memory read bandwidth. In fact, the 216 MB/s that it achieves approaches the 226 MB/s theoretical maximum bandwidth out of 3/2/2/2-clocked EDO DRAM on a 66 MHz bus. The reason for this exceptional performance is twofold. First, the Pentium Pro sports an out-of-order execution engine that is capable of reordering memory reads and removing the data dependencies implicit in the benchmark. By using register renaming and speculative memory reads, the Pentium Pro can implicitly batch and prefetch data reads, thus allowing it to issue memory reads as fast as the external memory system can handle them. Second, and more importantly, the Pentium Pro's pipelined, transaction-based system bus allows it to issue consecutive back-to-back data read transactions without incurring bus turn-around time and transaction set-up costs [9]. In contrast, the Pentium executes all memory operations in sequence, inserts extra data dependency stalls due to its small register set, and negotiates for the system bus on each read request.

The *Pro-200*'s main memory write bandwidth, in contrast, is exceptionally low—almost 18% slower than the write bandwidth of the *Endeav-100*, a system with identical DRAM and the same bus speed. To determine why this was the case, we instrumented the

benchmark with the Pentium Pro's built-in hardware counters [11]. For each 32-byte line of data written by the CPU, the counters indicate that two bus transactions take place: a writeback transaction and a read-for-ownership (RFO) transaction. The writeback is expected, since as the CPU stores a line into the cache it must displace an existing dirty line from a previous write. The RFO on the line about to be written is used to guarantee cache-coherency: the CPU must ensure that no other CPU in the system has a dirty copy of the line it is about to write. However, there is no need for a read-for-ownership transaction in our case, as the *Pro-200* is a single-processor system, and thus there are no other CPUs that could contain a dirty line; there is similarly no need to read the entire line, as we have seen in the L2 cache bandwidth that the write-back cache is intelligent enough not to load a line that is about to be entirely rewritten. Thus by interspersing a RFO transaction between each write, the available bus bandwidth drops significantly, as the CPU must renegotiate for the bus on each write, instead of performing back-to-back writes (as it does in the read case). Also, there is the bus overhead of the read-for-ownership transaction itself, and the bus turn-around time needed to switch between the transactions. Thus it seems that requiring the demonstrably high overhead of a RFO-based cache coherency protocol even when there is only one CPU in the system is a suboptimal design, as it severely cripples the available memory write bandwidth on the Pentium Pro.

It appears that Intel may have attempted to compensate for this design by including an undocumented "FastStrings" flag in one of the Pentium Pro's control registers: when FastStrings are enabled, the RFO transactions are converted to Invalidate transactions (so the cache does not read the new line but merely invalidates it in other CPUs). However, on a single-CPU system the Invalidate transaction is still unnecessary since there is only one cache on the bus. Additionally, this feature only improves DRAM write bandwidth slightly (about 5%) and only when certain string instructions are used to perform the write; converting the RFOs to Invalidates does not remove the bus transaction and renegotiation overhead, the major factor in the low DRAM write bandwidth.

#### **Kernel and Application Bandwidth Primitives**

From the *hbench-OS* measurements of the hardware capabilities of each machine, we can now generalize to the kernel primitive, bcopy, and from there to the application primitives such as file reread, mmap'd file reread, and TCP throughput. If each primitive were

completely dependent on the memory subsystem, we would expect to see similar patterns as were discovered with the hardware primitives; any deviation from these hardware patterns should indicate that the primitive showing the deviation has a non-memory-system dependent component.

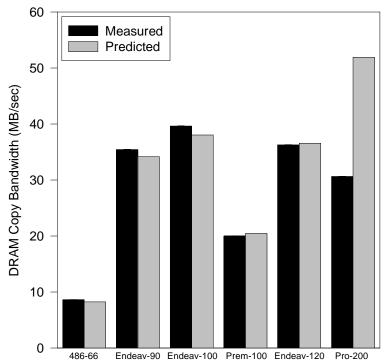

The primary kernel primitive relied upon by bulk-data application primitives is *bcopy*, used to transfer data around the kernel and between kernel and user space. Our bcopy benchmark uses the libc bcopy routine (identical to kernel bcopy in NetBSD) to copy both cached and uncached buffers in user space; this routine uses the x86 string instructions to efficiently move data. In the ideal case, we expect the results of the bcopy benchmark be one-half of the harmonic mean of the read and write bandwidths for each machine, since each byte copied requires one read and one write. However, when reads and writes are combined into copies, unexpected interactions can develop and cause the measured copy bandwidth to exceed or fall short of the half-harmonic mean prediction. These are the more interesting cases, as they illustrate optimizations or flaws in the hardware design, and how such design characteristics affect performance. In Figure 5, we present the results of the non-cached boopy test along with the half-harmonic means calculated from the raw bandwidth results in Figure 4; the cached bcopy results are similar. For all systems but the Pro-200, the graph shows the expected result that boopy bandwidth is directly correlated with the raw memory bandwidths. The measured results slightly exceed the predictions in most cases because the CPU (executing the x86 string operations) can issue the reads and writes back-to-back, without decoding and executing explicit load and store instructions.

Those machines with poor raw write bandwidth suffer in the bcopy test, since both read and write bandwidths have an equal influence on the copy bandwidth: for example, although it uses the same processor, the *Prem-100* achieves only half the bcopy bandwidth of the *Endeav-100*. This again demonstrates the effectiveness of an enhanced memory subsystem with a pipelined L2 cache and EDO DRAM at improving performance of operations requiring the movement of large quantities of data. The disappointing DRAM write performance of the Pentium Pro memory system completely negates the advantages of its advanced cache system, resulting in bcopy performance that is actually worse than that of some of the Pentiums. The *Pro-200*'s copy bandwidth also falls far short of our pre-

**Figure 5: bcopy Bandwidth (2MB buffers).** The memory systems determine performance on this benchmark: the predicted bcopy results (one-half of the harmonic mean of the read and write memory bandwidths) track closely with the measured numbers. When the 100 MHz Pentium is scaled to account for its higher bus clock rate, all the Endeavor-based Pentium systems achieve identical bcopy bandwidths, independent of processor speed. The *Prem-100*, with a slow memory system, attains only half the bandwidth of the identical processor with a newer memory system (*Endeav-100*). The *Pro-200*s dismal memory write bandwidth leads to poor bcopy performance; the actual performance falls far short of the predicted performance because of bus turnaround time not accounted for in the read bandwidth.

diction, since, when copying, the processor cannot issue back-to-back reads on the system bus, and must alternate read, write, and read-for-ownership transactions; each new transaction requires setup and negotiation overhead. Again, enabling FastStrings on the Pentium Pro has little effect (less than 1%) because the extra coherency transaction is still present.

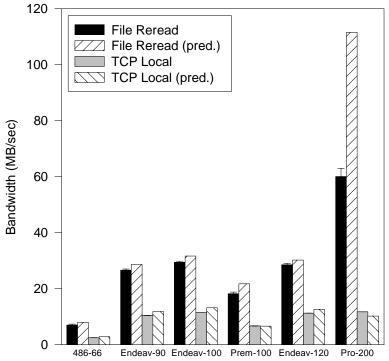

With this understanding of bcopy, we move on to consider the application-level datamanipulation primitives: cached file read, local TCP data transfer, and mmap'd file read. From the decomposition presented earlier in Figure 3, we expect that a significant component of the attainable bandwidths for each of these primitives is due to a dependence on the memory system, and thus we expect that the architectural changes that have enhanced memory system performance (such as faster, wider busses and pipelined caches) will enhance the performance of these primitives as well. We now examine each of these three