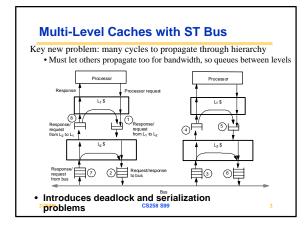

## **Deadlock Considerations** Sequential Consistency • Fetch deadlock: · Separation of commitment from completion even Must buffer incoming requests/responses while request outstanding greater now One outstanding request per processor => need space to hold p requests plus one reply (latter is essential) More performance-critical that commitment replace completion - If smaller (or if multiple o/s requests), may need to NACK - Then need priority mechanism in bus arbiter to ensure progress Fortunately techniques for single-level cache and ST bus extend · Buffer deadlock: - Just use them at each level - L1 to L2 queue filled with read requests, waiting for response from L2 i.e. either don't allow certain reorderings of transactions at any level - L2 to L1 queue filled with bus requests waiting for response from L1 - Latter condition only when cache closer than lowest level is write back Or don't let outgoing operation proceed past level before incoming invalidations/updates at that level are applied - Could provide enough buffering, or general solutions discussed later If # o/s bus transactions smaller than total o/s cache misses, response from cache must get bus before new requests from it allowed 2/28/Queues may need to support bypassing CS258 S99

## Multiple Outstanding Processor Requests So far assumed only one: not true of modern processors

- So far assumed only one: not true of modern processors

Danger: operations from same processor can complete

- Danger: operations from same processor can complete out of order

- e.g. write buffer: until serialized by bus, should not be visible to others

Uniprocessors use write buffer to insert multiple writes in succession

- multiprocessors usually can't do this while ensuring consistent serialization

- » exception: writes are to same block, and no intervening ops in program order

- Key question: who should wait to issue next op till previous completes

- Key to high performance: processor needn't do it (so can overlap)

Queues/buffers/controllers can ensure writes not visible to external world and reads don't complete (even if back) until allowed (more later)

- Other requirement: caches must be lockup free to be effective CS258 S99 5

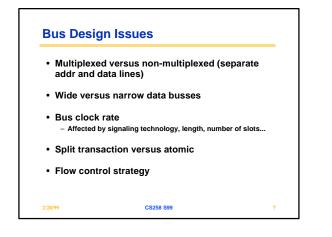

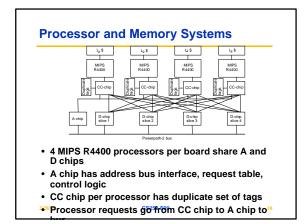

## SGI Powerpath-2 Bus

- Non-multiplexed, 256-data/40-address, 47.6 MHz, 8 o/s requests

- Wide => more interface chips so higher latency, but more bw at slower clock

- · Large block size also calls for wider bus

- Uses Illinois MESI protocol (cache-to-cache sharing)

CS258 89