CS252 **Graduate Computer Architecture** Lecture 2

Review of Cost, Integrated Circuits, Benchmarks, Moore's Law, & Prerequisite Quiz

> January 19, 2001 Prof. David A. Patterson Computer Science 252 Spring 2001

### **Review #1/3: Pipelining & Performance**

- · Just overlap tasks; easy if tasks are independent

- Speed Up  ${\mathfrak L}$  Pipeline Depth; if ideal CPI is 1, then:

$\text{Cycle Time}_{\underline{\text{unpipelined}}}$ Pipeline depth Speedup = Pipeline depth Cycle Time<sub>pipelined</sub> Cycle Time<sub>pipelined</sub>

- · Hazards limit performance on computers:

- Structural: need more HW resources

- Data (RAW, WAR, WAW): need forwarding, compiler scheduling

- Control: delayed branch, prediction

- · Time is measure of performance: latency or throughput

- · CPI Law:

PU time = Seconds = Instructions x Cycles x Seconds Program Program Instruction

### Review #2/3: Caches

- · The Principle of Locality:

- Program access a relatively small portion of the address space at any instant of time.

- » Temporal Locality: Locality in Time

- » Spatial Locality: Locality in Space

- · Three Major Categories of Cache Misses:

- Compulsory Misses: sad facts of life. Example: cold start misses.

- Capacity Misses: increase cache size

- Conflict Misses: increase cache size and/or associativity.

- Write Policy:

- Write Through: needs a write buffer.

- Write Back: control can be complex

- Today CPU time is a function of (ops, cache misses) vs. just f(ops): What does this mean to Compilers, Data structures, Algorithms?

Now, Review of Virtual Memory

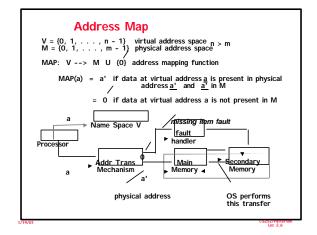

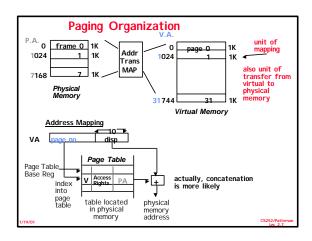

# Basic Issues in VM System Design 0 size of information blocks that are transferred from secondary to main storage (M) block of information brought into M, and M is full, then some region of M must be released to make room for the new block --> which region of M is to hold the new block --> placement policy 0 missing item fetched from secondary memory only on the occurrence of a fault --> demand load policy Paging Organization virtual and physical address space partitioned into blocks of equal size page frames

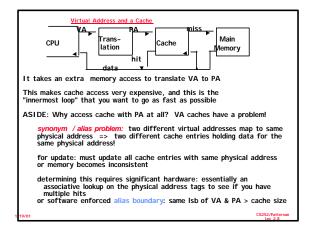

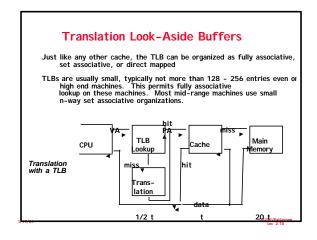

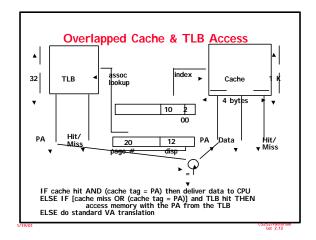

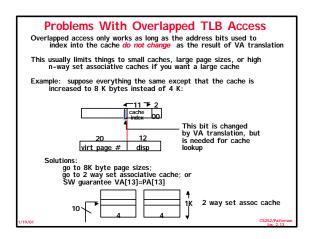

# **Reducing Translation Time**

Machines with TLBs go one step further to reduce # cycles/cache access

They overlap the cache access with the TLB access:

high order bits of the VA are used to look in the TLB while low order bits are used as index into cache

# SPEC: System Performance Evaluation Cooperative

- · First Round 1989

- 10 programs yielding a single number ("SPECmarks")

- Second Round 1992

- SPECInt92 (6 integer programs) and SPECfp92 (14 floating point programs)

- » Compiler Flags unlimited. March 93 of DEC 4000 Model 610:

spice: unix.c:/def=(sysv,has\_bcopy,"bcopy(a,b,c)=

memcpy(b,a,c)"

wave5: /ali=(all,dcom=nat)/ag=a/ur=4/ur=200

nasa7: /norecu/ag=a/ur=4/ur2=200/lc=blas

- · Third Round 1995

- new set of programs: SPECint95 (8 integer programs) and SPECfp95 (10 floating point)

- "benchmarks useful for 3 years"

- Single flag setting for all programs: SPECint\_base95,

CS252/Patterso

# SPEC: System Performance Evaluation Cooperative

- · Fourth Round 2000: SPEC CPU2000

- 12 Integer

- 14 Floating Point

- 2 choices on compilation; "aggressive" (SPECint2000, SPECfp2000), "conservative" (SPECint\_base2000, SPECfp\_base); flags same for all programs, no more than 4 flags, same compiler for conservative, can change for aggressive

- multiple data sets so that can train compiler if trying to collect data for input to compiler to improve optimization

52/Patters Lec 2.15

### **How to Summarize Performance**

Arithmetic mean (weighted arithmetic mean) tracks execution time:

S(T)/n or S(W\*T)

$S(T_i)/n$  or  $S(W_i*T_i)$

- Harmonic mean (weighted harmonic mean) of rates (e.g., MFLOPS) tracks execution time: n/S(1/R<sub>i</sub>) or n/S(W<sub>i</sub>/R<sub>i</sub>)

- Normalized execution time is handy for scaling performance (e.g., X times faster than SPARCstation 10)

- But do not take the arithmetic mean of normalized execution time, use the geometric mean:

(  $P T_j / N_j$ )<sup>1/n</sup>

S252/Patter

# SPEC First Round m: 99% of time in single

- One program: 99% of time in single line of code

- New front-end compiler could improve dramatically

Lec 2.17

# Impact of Means on SPECmark89 for IBM 550

| Ra        | AX:      | Time  | 2:         | <b>Weighted Time</b> |        |                 |  |

|-----------|----------|-------|------------|----------------------|--------|-----------------|--|

| Program   | Before   | After | Before     | After                | Before | After           |  |

| gcc       | 30       | 29    | 49         | 51                   | 8.91   | 9.22            |  |

| espresso  | 35       | 34    | 65         | 67                   | 7.64   | 7.86            |  |

| spice     | 47       | 47    | 510        | 510                  | 5.69   | 5.69            |  |

| doduc     | 46       | 49    | 41         | 38                   | 5.81   | 5.45            |  |

| nasa7     | 78       | 144   | 258        | 140                  | 3.43   | 1.86            |  |

| li        | 34       | 34    | 183        | 183                  | 7.86   | 7.86            |  |

| eqntott   | 40       | 40    | 28         | 28                   | 6.68   | 6.68            |  |

| matrix300 | 78       | 730   | 58         | 6                    | 3.43   | 0.37            |  |

| fpppp     | 90       | 87    | 34         | 35                   | 2.97   | 3.07            |  |

| tomcatv   | 33       | 138   | 20         | 19                   | 2.01   | 1.94            |  |

| Mean      | 54       | 72    | 124        | 108                  | 54.42  | 49.99           |  |

|           | Geometri | c .   | Arithmetic | rithmetic            |        | Weighted Arith. |  |

|           | Ratio    | 1.33  | Ratio      | 1.16                 | Ratio  | 1.09            |  |

1/19/01

Lec 2.18

#### **Performance Evaluation**

- · "For better or worse, benchmarks shape a field"

- · Good products created when have:

- Good benchmarks

- Good ways to summarize performance

- Given sales is a function in part of performance relative to competition, investment in improving product as reported by performance summary

- If benchmarks/summary inadequate, then choose between improving product for real programs vs. improving product to get more sales; Sales almost always wins!

- Execution time is the measure of computer performance!

1/19/01

252/Patterso Lec 2.19

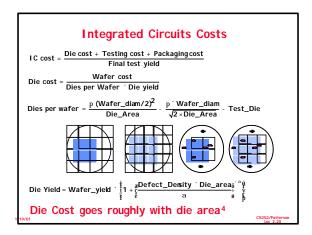

# Real World Examples Metal Line Wafer Defeat Area Direct Viold Dis Cont.

|           |        |      |        |      |     |       |     | Die Cost |

|-----------|--------|------|--------|------|-----|-------|-----|----------|

|           | layers | widt | 1 cost | /cm² | mm² | wafer |     |          |

| 386DX     | 2      | 0.90 | \$900  | 1.0  | 43  | 360   | 71% | \$4      |

| 486DX2    | 3      | 0.80 | \$1200 | 1.0  | 81  | 181   | 54% | \$12     |

| PowerPC 6 | 601 4  | 0.80 | \$1700 | 1.3  | 121 | 115   | 28% | \$53     |

| HP PA 710 | 0 3    | 0.80 | \$1300 | 1.0  | 196 | 66    | 27% | \$73     |

| DEC Alpha | 3      | 0.70 | \$1500 | 1.2  | 234 | 53    | 19% | \$149    |

| SuperSPAI | RC 3   | 0.70 | \$1700 | 1.6  | 256 | 48    | 13% | \$272    |

| Pentium   | 3      | 0.80 | \$1500 | 1.5  | 296 | 40    | 9%  | \$417    |

- From "Estimating IC Manufacturing Costs," by Linley Gwennap, Microprocessor Report, August 2, 1993, p. 15

> 52/Patters Lec 2.21

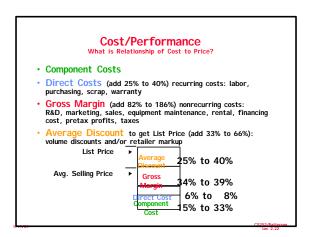

## Chip Prices (August 1993)

· Assume purchase 10,000 units

| Chip        | Area | Mfg    | . Price | Multi- | Comment             |

|-------------|------|--------|---------|--------|---------------------|

|             | mm   | 2 cost | t       | plier  |                     |

| 386DX       | 43   | \$9    | \$31    | 3.4    | Intense Competition |

| 486DX2      | 81   | \$35   | \$245   | 7.0    | No Competition      |

| PowerPC 601 | 121  | \$77   | \$280   | 3.6    |                     |

| DEC Alpha   | 234  | \$202  | \$1231  | 6.1    | Recoup R&D?         |

| Pentium     | 296  | \$473  | \$965   | 2.0    | Early in shipments  |

US252/Patter

## CS 252 Course Focus Understanding the design techniques, machine structures, technology factors, evaluation methods that will determine the form of computers in 21st Century Technology Programming Languages Applications 1 nterface Design (ISA) Computer Architecture: Instruction Set Design Organization Hardware/Software Boundary Compilers Operating Measurement & History Systems Evaluation

# **Topic Coverage**

Textbook: Hennessy and Patterson, Computer Architecture: A Quantitative Approach, 3rd Ed., 2001

Research Papers -- Handed out in class

1 week: Review: Fundamentals of Computer Architecture (Ch. 1), Pipelining, Performance, Caches, Virtual Memory, Cost, Ics

1 week: Memory Hierarchy (Chapter 5)

2 weeks: Fault Tolerance, Queuing Theory, Input/Output and Storage (Ch. 6)  $\,$

2 weeks: Networks and Clusters (Ch. 7)

· 2 weeks: Multiprocessors (Ch. 8)

Instruction Sets, DSPs, SIMD (Ch. 2), Vector Processors (Appendix B). 2 weeks:

1 week: Dynamic Execution. (Ch 3) • 1 week: Static Execution. (Ch 4)

Rest: Project stategy meetings, presentations, quizzes

## Lecture style

- 1-Minute Review

- 20-Minute Lecture/Discussion

- 5- Minute Administrative Matters

- · 25-Minute Lecture/Discussion

- 5- Minute Class Discussion or Break (water, stretch)

- · 25-Minute Lecture/Discussion

- · Instructor will come to class early & stay after to answer questions

Attention

Break "In Conclusion, ..." 20 min.

### Quizes

- Reduce the pressure of taking quizes

- Only 2 Graded Quizes:

- Tentative: Wed Mar 7th and Wed. Apr 18th

- Our goal: test knowledge vs. speed writing

- 3 hrs to take 1.5-hr test (5:30-8:30 PM, TBA location)

- Both mid-term quizes can bring summary sheet

- » Transfer ideas from book to paper

- Last chance Q&A: during class time day of exam

- Students/Faculty meet over free pizza/drinks at La Vals: Wed Oct. 18th (8:30 PM) and Wed Apr 18th (8:30 PM)

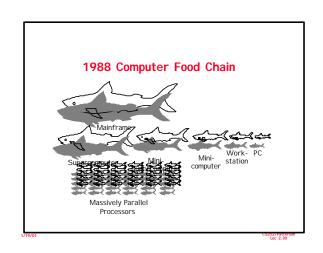

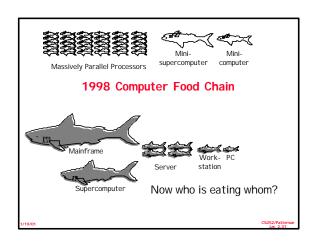

**Original** Big Fishes Eating Little Fishes

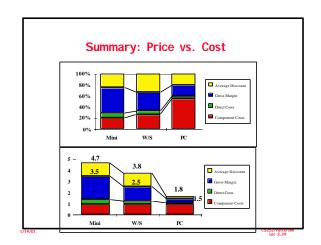

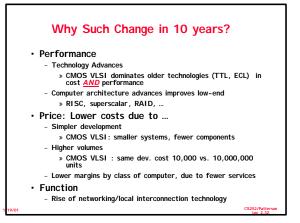

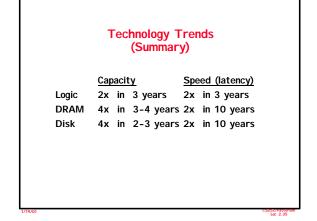

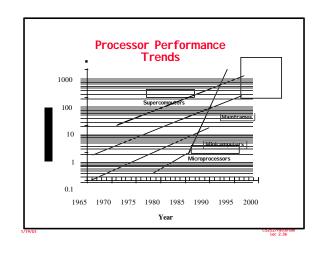

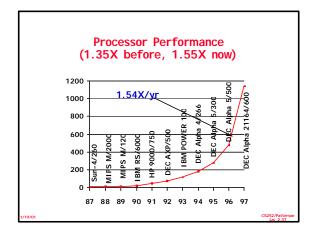

# Performance Trends (Summary)

- Workstation performance (measured in Spec Marks) improves roughly 50% per year (2X every 18 months)

- Improvement in cost performance estimated at 70% per year

CS252/Patte

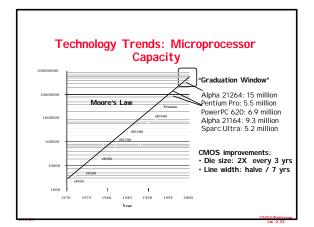

### Moore's Law Paper

- Discussion

- · What did Moore predict?

- · 35 years later, how did it hold up?

- In your view, what was biggest surprise in paper?

Lec 2.39

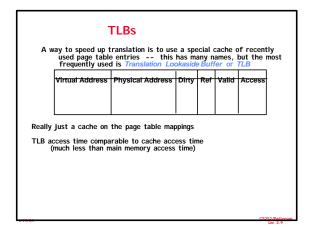

## Review #3/3: TLB, Virtual Memory

- Caches, TLBs, Virtual Memory all understood by examining how they deal with 4 questions: 1)

Where can block be placed? 2) How is block found?

What block is repalced on miss? 4) How are writes handled?

- · Page tables map virtual address to physical address

- TLBs make virtual memory practical

- Locality in data => locality in addresses of data, temporal and spatial

- TLB misses are significant in processor performance

funny times, as most systems can't access all of 2nd level cache without TLB misses!

- Today VM allows many processes to share single memory without having to swap all processes to disk; today VM protection is more important than memory hierarchy

## Summary

- Performance Summary needs good benchmarks and good ways to summarize performance

- Transistors/chip for microprocessors growing via "Moore's Law" 2X 1.5/yrs

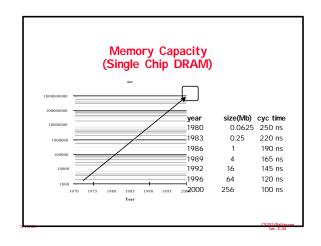

- Disk capacity (so far) is at a faster rate last 4-5 years

- DRAM capacity is at a slower rate last 4-5 years

- In general, Bandwidth improving fast, latency improving slowly

Lec 2.41